# INFN - Laboratori Nazionali di Frascati

Servizio Documentazione

LNF-87/15(NT)

15 Aprile 1987

V. Carlotti, L. Trasatti e M. Coli:

PROCESSORE CONTROLLORE VME MONOSCHEDA

### INFN - Laboratori Nazionali di Frascati Servizio Documentazione

LNF-87/15(NT) 15 Aprile 1987

### PROCESSORE CONTROLLORE VME MONOSCHEDA

V. Carlotti, L.Trasatti INFN - Laboratori Nazionali di Frascati, Casella Postale 13 - 00044 Frascati (Italia)

M. Coli Facoltà di Ingegneria Dipartimento di Elettronica, Università "La Sapienza", Roma (Italt)

### 1. - INFORMAZIONI GENERALI

Il progetto che descriveremo é stato sviluppato nel Centro di Calcolo dei Laboratori Nazionali di Frascati dell'INFN presso cui gli autori sono rispettivamente, associati i primi due, dipendente il terzo, nell' ambito del gruppo VET (Gruppo V).

Esso consiste nella progettazione e messa a punto dell'Hardware e del Software di una scheda di CPU per VME.

I capitoli successivi descrivono le caratteristiche di Hardware e la procedura di messa a punto del sistema.

### 1.1. - Caratteristiche

Le caratteristiche della scheda sono qui riportate:

- CPU 16 Bit MC 68000 a 8 MHz

- Compatibilità' con VMEbus D16-A24,con funzioni Master/Slave

- Funzioni di controllore di sistema VME

- Arbitro VMEbus a singolo livello (OPTION ONE)

- VMEbus TIMEOUT

- Reset di Sistema

- Clock di Sistema

- VMEbus REQUESTER

- Quattro criteri programmabili di rilascio del VMEbus

- MC 6850 porta seriale compatibile RS-232 C con connettore frontale 25 pin (CANNON). La porta e'configurabile come DATA COMUNICATION EQUIPMENT (DCE) e puo' essere connessa a DATA TERMINAL EQUIPMENT (DTE) senza modifiche.

2

Il BAUD RATE e' selezionabile tramite il jumper X9 da 300 a 9600 baud.

- Uno spazio di memoria direttamente indirizzabile di 16 Mbyte, che permette l'accesso globale a VMEbus, a quello locale(su scheda) e allo I/O locale.

- Memoria ripartita in:

- 512 K-byte RAM DINAMICA

- +16K-byte RAM STATICA in scheda aggiuntiva in sovrapposizione\*

- 512 K-byte RAM DINAMICA in scheda aggiuntiva in sovrapposizione\*

- EPROM di 128 K-byte

- Operazione esente da stati di WAIT per RAM STATICHE con tempi di accesso≤150 nS a 8 MHz.

- Possibilita' di cambiare la configurazione della mappa di memoria riprogrammando le PAL di decodifica.

- Registro di Controllo di Sistema

- Interrupt Handler VME fino a 7 livelli. Abort Switch e la linea ACFAIL\* sono connesse al livello di interruzione 7 non-mascherabile.

- Multiprotocol 7201 per colloquiare con VAX/VMS o altre periferiche seriali.

- <u>68230 Interfaccia parallela in sovrapposizione</u>

- <u>Interfaccia con FLOPPY-DISK in sovrapposizione capace di:</u>

- 1) Gestire dischi da 8" o da 5,25"

- 2) Lavorare in singola o doppia densita'

- 3) Effettuare precompensazione in scrittura su disco

- 4) Gestire Drive singola o doppia faccia

N.B.: La descrizione delle boards in sovrapposizione è trattata nelle relative note applicative a cui si rimanda il lettore.

\*Piggy-back (P/G).

## 1.2. - Specifiche

Le specifiche sono riportate in Tabella 1-1

TABELLA 1-1 - Specifiche

| **    | ********               | ****** | *******                | ****** | **** |  |

|-------|------------------------|--------|------------------------|--------|------|--|

| *     | TENSIONE DI            | oje    | +5Vdc (±5%)            | 2.5A   | *    |  |

| *     |                        | Þ¢     | +12Vdc (±5%)           | 0.5A   | *    |  |

| *     | ALIMENTAZIONE          | ર્જ    | +12Vdc (±5%)           | 0.5A   | *    |  |

| *     | 1 MAIVIEN VII MERCI VE | )c     | 122 (25 (25 ))         | ¥      | *    |  |

| ***   | *******                | *****  | ******                 | ****** | **** |  |

| *     |                        | *      |                        |        | *    |  |

| ۶ĸ    | DIMENSIONI             | **     | FORMATO EUROCARD DO    | PPIO   | *    |  |

| *     |                        | *      | (160mm*243 mm)         |        |      |  |

| *     |                        | *      | (10011111 - 10 111111) |        | *    |  |

| *     | CIRCUITO STAMPATO      | No.    | DOPPIO STRATO          |        | *    |  |

| *     | Checono simumino       | 渗      |                        |        | *    |  |

| * * * | ******                 | *****  | ********               | *****  | **** |  |

### 1.3. - Descrizione generale

La scheda oggetto della trattazione e' stata progettata per operare sia come sistema stand-alone, sia come singolo Master/Controllore di Sistema in un sistema VME, o come una delle Unità di Processamento in un sistema multiprocessore su VMEbus.

Questa scheda contiene i seguenti moduli funzionali:

- Memoria locale

- Indicatori e controllo stato

- Porte seriali RS-232 C

- Interfaccia (I/F) VMEbus

- System Interrupts

### Memoria Locale

## 512K-byte RAM DINAMICA

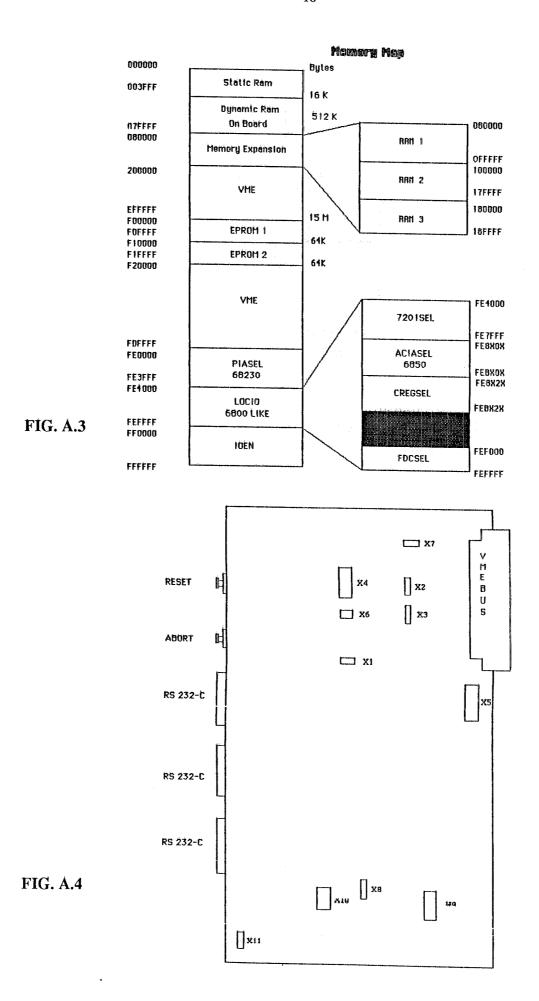

La memoria sulla scheda copre gli indirizzi da 000000 a 7FFFF HEX.

### Indicatori e controllo stato

Nella presente versione sono previsti solo i pulsanti di reset e abort con funzioni di controllo dello stato della scheda. Sono stati omessi per motivi di semplicità circuitale i led indicatori RUN, HALT e FAIL previsti in futuro.

### Porta seriale

E' prevista una porta seriale RS-232 C per l'attacco ad un terminale e una seconda porta seriale

per il colloquio con VAX/VMS.Entrambe possono essere utilizzate come porte di down loading di programmi e dati per questa scheda.E' prevista una successiva versione con una ulteriore porta seriale per consentire il collegamento con una stampante.

#### I/F VMEbus

La scheda e' stata progettata per essere completamente interfacciata a VMEbus. Provvede all'arbitraggio del bus su singolo livello e fornisce un clock di sistema a 16 MHz. Questo permette ai sistemi di essere configurati senza l'uso di una scheda, addizionale, con funzioni di controllore di sistema.

Il bus interno di interconnessione fra la memoria su scheda,il processore e le funzioni di I/O è connesso al VMEbus solo durante l'accesso alle risorse esterne alla scheda.

### Interruzioni di sistema

La scheda di CPU puo' rispondere a sette livelli di interruzione a priorita' dal VMEbus. In aggiunta un livello e' assegnato alle risorse sulla scheda.Il livello 7 è infatti condiviso anche da SYSFAIL IRQ\*, da ACFAIL\* e dal pulsante di ABORT.

## 2. - DESCRIZIONE FUNZIONALE

#### 2.1. - Generalità

Questo capitolo descrive la scheda suddividendola in blocchi funzionali.La messa in funzione dell'Hardware è descritta in appendice A.

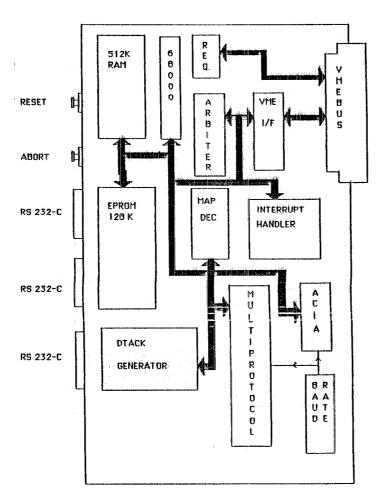

La scheda CPU V1 è un modulo completo che contiene memoria, I/O e funzioni di controllo.Il diagramma a blocchi semplificato è in Figura A.1 in appendice A.

Come già descritto la RAM su scheda è costituita da 512-Kbyte di RAM DINAMICA. Il tempo di risposta dell' Asyncronous Data Transfer Acknoledge (DTACK) puo' essere selezionato attraverso il jumper X4 per permettere l'uso di molti tipi diversi di RAM. La RAM su scheda non è accessibile dal VMEbus.

Il cuore della scheda è costituito dalla CPU MC 68000 operante a 8 o10 MHz.Il Bus locale provvede alla interconnessione fra la CPU, la ROM,l a RAM, le porte seriali, la porta parallela (P/G) e i registri di controllo. Il bus locale permette alla scheda di svolgere le proprie funzioni di processamento mentre un altro master agisce contemporaneamente sul VMEbus.

La porta di I/O seriale RS 232-C consente all'utente di connettere un terminale al fine di colloquiare con la scheda.Le linee controllo e dati della porta seriale sono disponibili sul frontale tramite un connettore CANNON 25 poli. Vedi Tabella A.7. L'interfaccia CPU porta è realizzata tramite MC 6850 ACIA.

L'interfaccia con il VMEbus permette alla scheda di colloquiare con altri sistemi presenti sul Bus. In particolare consente la disponibilità di risorse esterne alla scheda come ad esempio altri moduli CPU-Board, RAM aggiuntiva, controllori intelligenti di I/O.

L'interfaccia VMEbus supporta l'intero spazio di indirizzamento di 16 Mbyte della CPU MC 68000.

La CPU guadagna l'accesso al VMEbus richiedendo il possesso del Bus attraverso le linee di Bus Request BRO\*+BR3\*.

Il livello di priorità è selezionabile attraverso il jumper X10 in uno fra 4 livelli. Dopo aver assunto il controllo del VMEbus il modo di rilascio del Bus è controllato dal campo dei bit di rilascio del Bus del Registro di Controllo del Modulo (MCR).

La scheda ha la caratteristica di tenere sotto controllo la linea ACFAIL\* del VMEbus al fine di permettere all'utente per mezzo di routine su EPROM di realizzare al power-up o al power-down una serie di azioni; in particolare, nel caso di power-down, il salvataggio su RAM non volatile o disco di dati essenziali.

#### Contollore di sistema

La scheda puo' essere configurată come controllore di sistema al fine di provvedere alle seguenti funzioni:

- Arbitraggio su singolo livello del VMEbus. Quando la scheda è il controllore di sistema accetta le richieste di possesso del bus sul livello 3, asserisce il grant sulla linea 3 in Daisy-chain BG3IN\*/BG3OUT\*.

- Clock di sistema. Quando è configurata per una frequenza di clock di 8 MHz la scheda fornisce un segnale di 16 MHz con fan-out 10 TTL agli altri moduli VME.

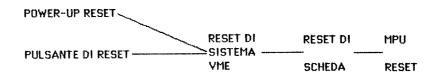

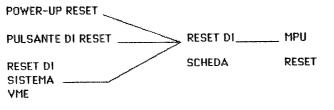

- Reset. Al reset la scheda pilota la linea SYSRESET\* sul VMEbus come previsto per il controllore di sistema.

- **Bus Time-out.** Viene generato il segnale di BERR\*(Bus Error) quando viene indirizzato sul VMEbus un dispositivo non esistente o che non risponde.Il Time-out puo' essere eventualmente escluso attraverso il jumper X11; altrimenti viene attivato dopo 200 μS. Ovviamente in un sistema multiprocessore solo una CPU-Board puo' essere configurata come controllore di sistema.

### 2.2. - Descrizione dettagliata

## Processore, memoria e decodifica

La sezione processore della scheda contiene la CPU MC 68000, l'oscillatore di clock, la logica di reset e di abort e relativi pulsanti sul pannello. La logica di reset fornisce vari tipi di reset come mostrato in Figura A.2.

La memoria su scheda puo' essere così suddivisa:

- 512 Kbyte di RAM DINAMICA

- 128 Kbyte di EPROM

Durante i primi quattro cicli della CPU dopo l'applicazione dell'alimentazione o il system/board reset, i dati sono prelevati dalle prime 8 locazioni di EPROM. Questi quindi debbono contenere il valore iniziale dello Stack Pointer che verrà caricato in SSP (Supervisor Stack Pointer) e l'indirizzo di partenza del programma utente che verrà caricato in PC (Program Counter).

La logica di decodifica della memoria è responsabile della selezione e controllo di vari moduli della scheda. La Mappa di Memoria è riportata in Appendice A; Fig. A4.

All' inizio di ogni ciclo di CPU, il Map Decoder determina il tipo di ciclo:

- Reset. Per i primi 4 cicli dopo il reset sono selezionate le EPROM all'indirizzo F00000.

- Interrupt acknoledge. E' selezionato l'Interrupt Handler per determinare quale interrupt può essere riconosciuto (attivazione segnale [FCHI\*]°°).

- Normale. La decodifica in ciclo normale avviene come segue:

- 1) Memoria locale da 000000H a 07FFFFH attivando il segnale [RAMSEL\*]. Con l'espansione in sovrapposizione la zona RAM su scheda è estesa sino a 1FFFFF.

- 2) VMEbus per quegli indirizzi appartenenti all'area VME. Il segnale [VMESEL\*] attiva il requester al fine di ottenere il possesso del bus; dopo che è stata accordato viene selezionata la I/F VMEbus.

- 3) I/O Locale. Viene selezionato uno dei seguenti dispositivi: ACIA, MULTIPROCOL 7201, Registro di Controllo, espansioni in P/G BACK diverse dalla memoria.

## I/O locale, Registro di controllo del modulo (MCR) e Timeout

La porta seriale (ACIA Asyncronous Communication Interface Adapter) è costituita dal circuito MC 6850 ACIA, dal connettore RS 232-C (tipo Cannon 25 poli) dall' interfaccia e dal generatore di Baud-rate. La porta è configurata come DCE e va connessa a un DTE. La Tabella A.7 in appendice riporta i segnali del connettore della porta.

Lo MCR contiene 6 bits per controllare varie funzioni della scheda come descritto di seguito. Il suo indirizzo è FE8020.

<sup>°°</sup>La parentesi quadra distingue i segnali interni alla scheda.

Tabella 2.1 - Registro di Controllo del Modulo

| k   | 7 6          |          | 5         | 4           | 3       |        | 2      |              | 1     |      | 0          | *    |  |

|-----|--------------|----------|-----------|-------------|---------|--------|--------|--------------|-------|------|------------|------|--|

| *** | *****        | *****    | *****     | *****       | ****    | ***    | ***    | ****         | ***   | **   | *****      | ***  |  |

| *   | PRM * FD0    | CGR * S  | SFIE *    | FAIL *      | 0       | *      | 0      | *BR          | .C1   | *    | BRC0       | *    |  |

| *** | ******       | *****    | *****     | ****        | ****    | ****   | ***    | ****         | ***   | **   | *****      | ***  |  |

|     | PRM          | - Modo   | Protect   |             | (O I    | Disabi | ilitat | o/1 <i>A</i> | Abili | tato | <b>)</b>   |      |  |

|     | <b>FDCGR</b> | - Flopp  | y disk c  | ontoller g  | rant    |        |        |              |       |      |            |      |  |

|     | SFIE         | - Abili  | tazione   | dell'interr | upt di  | syste  | m fa   | il           |       |      |            |      |  |

|     |              | 0 Int.   | Disabil   | itato/ 1 In | t. Abi  | litato |        |              |       |      |            |      |  |

|     | FAIL         | - Abilit | azione d  | lel segnale | e VMI   | Ebus S | SYS    | FAIL*        | k     |      |            |      |  |

|     |              | (0/1dis  | abilitato | /abilitato) | . Usate | per o  | even   | tuale        | diag  | nos  | tica inizi | iale |  |

|     |              |          |           |             |         |        |        |              |       |      |            |      |  |

|     | BRC1, B      | RC0 B    | it di con | trollo di r | ilascio | del b  | ous    |              |       |      |            |      |  |

|     |              | BRC1     | BRC0      |             |         |        |        |              |       |      |            |      |  |

|     |              | 0        | 0         | ROR -       | - Relea | ase or | ı req  | uest         |       |      |            |      |  |

|     |              | 0        | 0         | RBC ·       | Relea   | ise or | ı bus  | s clear      | •     |      |            |      |  |

|     |              | 1        | 0         | RWD         | -Relea  | se wl  | ien (  | lone         |       |      |            |      |  |

|     |              | 1        | 1         | RNE .       | Relea   | se ne  | ver    |              |       |      |            |      |  |

| **  | *****        | ******   | ****      | ****        | ****    | ***    | ***    | ****         | ***   | **:  | *****      | **** |  |

Il Timeout sul bus locale (Whatch dog Timer), è usato per assicurare che la CPU non rimanga inultimente a lungo in attesa del segnale di acknoledge.

Quando la CPU ha generato un Data Strobe e sono trascorsi 200 µS senza che sia stato ricevuto un data acknoldge [DTACK] viene generato un Timeout e quindi un segnale di Bus Error.II Timeout è abilitato o meno, per ogni ciclo di CPU, dal Jumper X14.

## Arbitraggio del VMEbus, Requester e Interfaccia

La tecnica di arbitraggio del bus è usata dai moduli master per richiedere, riconoscere e accordare il possesso del bus. Ogni scheda CPU V1, contiene la logica di arbitraggio del bus, ma soltanto quella configurata come System Controller realizza le funzioni di arbitraggio.

Quando una richiesta è ricevuta dall' arbitro e il bus non è occupato l'arbitro attiva una linea di Bus-Grant e aspetta che il requester cui è stato accordato il bus attivi il segnale di Bus Busy. L'arbitro quindi disattiva il Bus-Grant e il ciclo di arbitraggio è completato.

L'arbitro installato sulla scheda è un arbitro a singolo livello che arbitra le richieste di bus solamente sul livello 3.Quando questi è abilitato (attraverso il jumper X12) la scheda deve essere posta nello spazio1 del rack VMEbus in modo che risulti la prima scheda nella daisy-chain di

arbitraggio. In questa configurazione il Bus Requester sulla scheda è il primo della daisy-chain e quindi ha la più alta priorità.

Il requester VMEbus ha la funzione di richiedere e di effettuare il rilascio del VMEbus dipendentemente dai bit di controllo del rilascio [BRC0,BRC1].

Quando viene richiesto il possesso del bus, il requester realizza un ciclo di arbitraggio. Se il bus è occupato al momento della richiesta la CPU aspetterà un tempo indefinito se il local Timeout è disabilitato, oppure 200µs se questi è abilitato.

Quando il ciclo di arbitraggio è completo ed è stata accordato il possesso del bus viene abilitata l'interfaccia VMEbus. Questa normalmente attiva sul bus le 23 linee di indirizzamento e il codice di Address Modifier (Vedi TAB. 2.2). La direzione del trasferimento dati è indicata dal segnale [WRITE]. Vengono inoltre prodotti uno o entrambi i Data Strobe [DS0\*, DS1\*] oltre all'Address Strobe[AS\*]. L'interfaccia aspetta quindi il segnale di Acnoledge [DTACK] o il segnale di BusError [BERR\*] dal modulo slave al fine di completare il ciclo. Quando il requester riceve un Bus-Grant al livello 3 [BG3IN\*] selezionato dal jumper X12, (unico nella presente versione, espandibile in future versioni) e non sta richiedendo l'uso del bus ,attiva il segnale di bus grant out [BG3OUT\*].

Le linee [BGXIN\*, BGXOUT\*] non jumperate (tutte escluso la 3 nella versione attuale) sono direttamente cortocircuitate. Nel ciclo seguente del VMEbus, se è stato rilasciato il bus, occorre richiedere un nuovo ciclo di arbitraggio per ottenere il possesso del bus. Se il bus non è stato rilasciato tutto ciò non è necessario e il bus può essere utilizzato immediatamente.

Tabella 2-2 - Address Modifier

| ***** | ****         | ****                    | ****         | **** | **** | *****                   | *************                            |

|-------|--------------|-------------------------|--------------|------|------|-------------------------|------------------------------------------|

| HEX   |              | AM4                     |              |      |      | AM0                     |                                          |

| 3E    | H            | H                       | $\mathbf{H}$ | Η    | Н    | L                       | Accesso area programma stato supervisore |

| 3D    | H            | H                       | H            | Н    | L    | Н                       | Accesso area dati stato supervisore      |

| 3A    | H            | H                       | H            | L    | H    | Ĺ                       | Accesso area programma stato utente      |

| 39    | $\mathbf{H}$ | H                       | H            | L    | L    | $\overline{\mathbf{H}}$ | Accesso area dati stato utente           |

| 36    | H            | H                       | L            | H    | H    | Ĺ                       | Indefinito                               |

| 35    | H            | H                       | L            | H    | L    | H                       | Indefinito                               |

| 32    | H            | H                       | L            | L    | H    | Ĺ                       | Indefinito                               |

| 31    | H            | H                       | L            | L    | L    | H                       | Indefinito                               |

| 2D    | H            | L                       | H            | H    | L    | H                       | Accesso Short I/O stato supervisore(*)   |

| 29    | Н            | L                       | Н            | Ĺ    | Ĺ    | $\hat{H}$               | Accesso Short I/O stato utente(*)        |

| 25    | Н            | L                       | L            | H    | Ī.   | $\hat{H}$               | Indefinito                               |

| 21    | H            | $\overline{\mathtt{L}}$ | Ĺ            | Ĺ    | Ĺ    | H                       | Indefinito                               |

<sup>(\*)</sup> Quando il processore indirizza una locazione tra FF0000 e FFFFFF uno di questi codici viene posto sul VMEbus.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

## Rilascio delVMEbus

Il modo in cui il bus viene rilasciato è determinato dai bit di controllo [BRC0, BRC1] del rilascio del Control register (MCR):

ROR Release On Request. Quando è stato accordato il possesso del bus questo viene rilasciato quando un altro possibile Bus Master ne richiede l'uso. Questo modo è selezionato al reset e dovrebbe essere usato in sistemi in cui questa scheda è il principale utente del bus.

RWD Release When Done. Quando è stata accordato il possesso del bus questo viene rilasciato immediatamente dopo l'inizio del ciclo.L'arbitraggio del ciclo successivo può avvenire concorrentemente con il completamento del ciclo presente. L'arbitraggio è richiesto durante ogni ciclo del bus della scheda.Questo modo è utile per garantire la pronta disponibilità del bus ad altri master presenti nel sistema.

RNE Release Never. (Non standard). Quando è stato accordato il possesso del bus, questi non viene più rilasciato finchè il processore non cambia il bit di controllo di rilascio del bus.

RBC Release on Bus Clear. (Non standard). Quando è stato accordato il possesso del bus questi viene rilasciato soltanto attivando il segnale VMEbus Bus Clear(BCLR\*). In sistemi forniti di arbitro multi-livello, questo modo selettivamente nega o meno l'accesso ad un master richiedente dipendentemente dal suo livello di richiesta. L'accesso è negato a richiedenti aventi livello di priorità minore o uguale di questa scheda (3) finchè questo modo è selezionato. Gli arbitri a singolo livello, come quello presente sulla CPU V1 non pilotano la linea BCLR\*, quindi i modi RBC e RNE hanno effetti equivalenti.

### Bus error

Il segnale interno di Bus Error [MPUBERR\*] provoca l'entrata della CPU in una sequenza di eccezione. Questo segnale può divenire attivo o per un errore sul VMEbus o per l'attivazione del Watch dog Timer locale.

BERR\* sull' interfaccia VMEbus si attiva nelle seguenti condizioni:

- Il dispositivo indirizzato sul VMEbus ha rilevato condizioni di errore.

- Non è stato ricevuto prima del VMEbus Timeout nè DTACK\* nè BERR\*.

### Gestione delle interruzioni

Possiamo dividere gli interrupt su scheda in due tipi ;tipo A e B.

Quelli di tipo A raggruppano ACFAIL, SYSTEM FAIL, ABORT e sono tutti interrupt NMI al livello 7.

Il gruppo B è composto dai segnali da IRQ1\* a IRQ7\* del VMEbus.I vettori per questi interrupts sono letti dal VMEbus durante il ciclo di interrupt acknoledge in cui la scheda ottiene il possesso del bus e l' Interrupt Handler pone il livello da riconoscere, in forma codificata, sui bit più bassi delle linee indirizzo [A1, A2, A3] e attiva la linea di Interrupt Acnoledge [IACK\*] con gli opportuni segnale di sequenza.Il dispositivo che ha richiesto interruzione pone il vettore di

interruzione sul byte dati basso [D0+D7] e genera [DTACK]. Questo vettore è quindi usato come puntatore alla tavola dei vettori di eccezione della CPU.

## APPENDIX A1

## A-1 - Configurazione dell'Hardware

La Tabella A.1 riporta la sigla e la funzione dei jumpers e dei pulsanti presenti sulla scheda e la Figura A3 la loro posizione.

Tabella A.1 - Funzione dei Jumpers e Switchs

| ********                               | *****               | *****       | *******                    | ******                                         |

|----------------------------------------|---------------------|-------------|----------------------------|------------------------------------------------|

| *JMP/SW                                | *                   | FUNZIO      |                            | *                                              |

| *********                              | *****               | ******      | ******                     | ******                                         |

| * X1                                   | * LI                | VELLO DI    | INTERRUPT                  | LOCALE *                                       |

| *********                              | *****               | ******      | ********                   | ******                                         |

| * X2                                   | * SE                | ELEZIONE I  | DI AM 3                    | *                                              |

| *******                                | *****               | *******     | *****                      | ******                                         |

| * X3                                   | * PU                | JLSANTE D   | I ABORT                    | *                                              |

| **********                             |                     |             |                            |                                                |

| * X4<br>*********                      | * SE                | ELEZIONE TE | EMPO DI ACCESSO            | ORAM *                                         |

| •                                      |                     |             |                            |                                                |

| * X5<br>*********                      | " Li                | VELLO   DI  | INTERRUPT V                | ME *                                           |

| * X6                                   |                     | JLSANTE DI  |                            | ***************************************        |

| *******                                | )                   | )LOAN       | ************               |                                                |

| * X7                                   |                     | LOCK DI SIS |                            | » <b>!</b> c                                   |

| ********                               | *****               | *****       | *****                      | *******                                        |

| * X8                                   |                     | PU CLOCK    |                            | **                                             |

| ********                               | *****               | *******     | ******                     | ******                                         |

| * X9                                   | * SE                | LEZIONE BA  | AUDRATE                    | ale.                                           |

| *******                                | _                   |             |                            |                                                |

| * X10                                  | * LI                | VELLO DI    | RICHIESTA BI               | JS ARBITER *                                   |

| ************************************** |                     |             |                            |                                                |

| * X11<br>*********                     | SE<br>*****         | LEZIONE VN  | AE TIMEOUT                 | 計<br>Ale ale ale ale ale ale ale ale ale ale a |

| * X12                                  |                     |             |                            |                                                |

| <b>11</b> 2                            | 1 <i>A</i><br>***** | ********    | E ARBITRAGGIO \<br>******* | /IVIE<br>********                              |

| * X13                                  |                     |             | CHIESTA BUS                |                                                |

| ******                                 | *****               | *****       | *******                    | ******                                         |

| * X14                                  | * SE                | LEZIONE TIM | MEOUT LOCALE               | <b>*</b>                                       |

| ********                               | *****               | *****       | ********                   | ******                                         |

| * X15                                  | * S                 | ELEZIONE    | RESET DI SIST              | TEMA *                                         |

| *******                                | ******              | ******      | **********                 | ***********                                    |

## - Abilitazione livello interrupt locale (jumper X1)

Il jumper X1, abilita se inserito, il segnale di SYSTEM FAIL\* ad effettuare una interruzione sul livello 7.

## - Selezione di AM 3 (jumper X2)

Il jumper X2 e' usato per selezionare lo stato della linea AM 3 durante il trasferimento dati in VME.

La configurazione standard e' di "1" logico.

La configurazione alternativa si ottiene ponendo AM3 a "0" logico rendendo disponibili codici definibili dall'utente.

### - Pulsante di abort (X3)

Quando viene premuto causa un interrupt non mascherabile al livello 7 del processore MC 68000. Il software utente puo' essere utilizzato per realizzare le opportune azioni al fine di riportare il sistema allo stato iniziale.

## - Selezione del tempo di accesso Ram/Rom (jumper X4)

Il jumper X4 e' usato per selezionare il corretto ritardo al fine di compensare il tempo di accesso alla memoria RAM/ROM.Possono quindi essere usati molti tipi di memorie RAM/ROM nella memoria locale.

Si possono comparare i tempi di accesso delle RAM/ROM installate con quelli elencati in Tabella A.2 e configurare i jumpers come mostrato di seguito.

Tabella A.2 - Configurazione Jumper X4

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* WAIT X4 MPU 8 MHz MPU 10MHz 0 0 - 100 nS 0 -165 nS a a ROM 100-200 nS 1 165-290 nS b b ROM 200-300 nS 2 290-415 nS c c ROM 415-550 nS 300-400 nS 3 d--d ROM 0 0 - 100 nS 0 - 165 nS e e RAM 1 100-200 nS 165-290 nS f fRAM 200-300 nS 2 290-415 nS g--gRAM

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

## - Abilitazione livello interrupt VMEbus (jumper X5)

Il jumper X5 e' usato per abilitare selettivamente le linee di interruzione del VMEbus.La Tabella A.3 indica la configurazione dei jumpers.

Questa configurazione permette alla CPU sulla scheda di essere interrotta da tutte le linee di interrupts del VMEbus.

Se altre CPU sono presenti su VMEbus alcuni jumpers devono essere rimossi affinche' non vi siano più Master che rispondano ad un determinato interrupt.

Non ci possono essere duplicazioni di livelli di interrupt abilitati tra le CPU. Se un livello di interrupt non deve essere servito occorre rimuovere il corrispondente jumper di interrupt.

La tabella riporta ognuno dei livelli di interrupt e i terminali che devono essere connessi corrispondentemente.

## Tabella A.3 - Jumper X5

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

a--a IRQ1\*

b--b IRQ2\*

c--c IRQ3\*

d--d IRQ4\*

e--e IRQ5\*

f--f IRQ6\*

g--g IRQ7\*

### - Pulsante di reset (X6)

Quando viene premuto forza il circuito di controllo e temporizzazione allo stato di inizializzazione. Se la scheda CPU è il controllore di sistema il jumper X15 deve essere connesso.

### - Clock di sistema (jumperX7)

Il jumper X7 ha la funzione di abilitare il generatore di clock interno come clock di sistema a 16 MHz. Il fan-out e' di 10 unita' TTL.

Il jumper deve essere rimosso se sono presenti altri System Clock Generator attivi.

## - CPU Clock (jumperX8)

Il processore installato e' un 8 MHz, comunque la scheda puo' essere configurata per accettare una CPU a 10 MHz, (Tabella A.4).

Tabella A.4 - Configurazione Jumper X8

- Selezione Baud-rate (jumper X9)

Il jumper X9 e' usato per selezionare il BAUD-RATE per la porta seriale. Vedi Tabella A.5.

Tabella A.5 - Configurazione Jumper X9

- Selezione del livello di Bus Arbiter Request (jumper X10)

Il jumper X10 e' usato per assegnare il livello con cui la CPU richiedera' il possesso del BUS.

Quando la scheda e' configurata come controllore di sistema essa monitorizza solo un livello di Bus Request. In questo caso il livello di richiesta deve essere assegnato come livello 3.

Quando invece la scheda e' usata insieme con un altra System Controller Board che supporta tutti i 4 livelli di Bus Request, qualsiasi livello puo' essere selezionato, (il livello 3 ha la priorita' più alta).

**Tabella A.6** - Configurazione Jumper X10

| a a | REC | QUEST LE | EVEL | 0 |

|-----|-----|----------|------|---|

| b b | 11  | ''       | 11   | 1 |

| c c | 11  | 17       | **   | 2 |

| ld  | 11  | 11       | **   | 3 |

- Selezione del VME Timeout (jumper X11)

Il jumper X11 e' usato per abilitare/disabilitare il contatore del VME Bus Timeout.Il segnale di BUS ERROR (BERR\*) e' generato per ogni ciclo che non e' stato completato dopo 200μS. La presenza di BERR\* causa una sequenza di eccezione per bus error.

- Abilitazione arbitraggio su VMEbus (jumper X12)

Quando il jumper è connesso abilita la CPUV1 come controllore di sistema ed in particolare ne abilita le funzioni di arbitro di sistema.

- Selezione del livello della richiesta del Bus Arbiter (jumper X13) Vedi quanto detto per il jumper X 10

- Selezione del local Timeout (jumper X14)

Vale quanto detto per il jumper X12 ma con bus error generato sulla scheda.

Selezione del Reset di sistema (jumper X15)

Quando il jumper X15 è connesso abilità il segnale interno alla scheda [RSTOUT] a generare il segnale di System Reset SYSRES\*che giunge attraverso il VMEbus agli altri moduli del sistema.

Tabella A.7 - Porta Seriale.

| NUM. PIN | SEGNALE | FUNZIONE         |

|----------|---------|------------------|

| 2        | TXD     | Trasmit Data     |

| 3        | RXD     | Receive Data     |

| 20       | CTS     | Clear To Send(*) |

| 7        | GND     | Ground           |

\*\*\*\*\*\*\*\*\*\*\*\*\*\*

\*\*\*\*\*\*\*\*\*\*\*\*\*\*

## Ringraziamenti

Si ringrazia il Laboratorio fotografico dei Laboratori Nazionali di Frascati dell'INFN e in particolare il Sig. D. Riondino per la cura posta nella sbrogliatura e nella realizzazione del circuito stampato.

<sup>(\*)</sup> Questo segnale non è presente sulla porta seriale 3

FIG. A.1

SCHEDA CONFIGURATA COME CONTROLLORE DI SISTEMA

SCHEDA NON CONTROLLORE DI SISTEMA

FIG. A.2