# ISTITUTO NAZIONALE DI FISICA NUCLEARE Laboratori Nazionali di Frascati

LNF-81/48(R) 28 Luglio 1981

M. Serio: CONVERTITORE DIGITALE ANALOGICO A 8 CANALI, 12 BIT PER IL BUS DI ADONE (MULTIDAC).

Servizio Documentazione dei Laboratori Nazionali di Frascati INFN - Laboratori Nazionali di Frascati Servizio Documentazione

> LNF-81/48(R) 28 Luglio 1981

M. Serio: CONVERTITORE DIGITALE ANALOGICO A 8 CANALI, 12 BIT PER IL BUS DI ADONE (MULTIDAC).

#### 1. - INTRODUZIONE.

L'alimentazione degli elementi magnetici di Adone e di parte di quelli del canale di trasporto Linac-Adone (bobine di deflessione: BD) viene pilotata da calcolatore per mezzo di convertitori digitali analogici a diversi gradi di risoluzione e precisione. Tranne che per gli impianti di alimentazione dei magneti curvanti, tutti gli altri riferimenti vengono generati in singoli moduli DAC di vari tipi, raggruppati in tre stazioni tipo DAC del Bus di Adone (1).

Per fronteggiare crescenti esigenze di accuratezza nel controllo dell'orbita di equilibrio del fascio di Adone il sistema di correzione di orbita chiusa, attualmente formato da 7 bobine di correzione sui quadrupoli (BCQ), verrà integrato da 5 ulteriori BCQ e da 12 bobine di correzione sui magneti curvanti (BCM). Si vuole inoltre estendere il controllo tramite calcolatore ad elementi precedentemente controllati in modo indipendente (steering del Linac, magnete spettrometro del Linac, magnete pulsato a 6°, etc.) e ad altri impianti in corso di installa zione (nuovo sistema di iniezione del Linac, nuovi alimentatori dei magneti dell'ottica di trasporto). L'approccio finora seguito, quello cioè di un modulo DAC per canale, risulta inadeguato alle nuove esigenze per motivi di ingombro e di costo. E' stato quindi deciso di sviluppare il progetto di un'unità DAC a 8 canali di uscita, compatibile con le caratteristiche delle unità finora utilizzate e con il Bus di Adone, che rimane la principale interfaccia fra il complesso degli impianti di Adone ed il calcolatore di controllo.

# 2. - ARCHITETTURA GENERALE.

L'impostazione del progetto ha risentito della importante considerazione preliminare che le uscite dei DAC del Bus servono - nella quasi totalità - come tensioni di riferimento per alimentatori con pilotaggio remoto in tensione, per i quali non vi sono vincoli stringenti di veloci tà di risposta, anche quando siano richieste rampe di pilotaggio con risoluzione elevata. Si è quindi ricorsi alla tecnica del refresh periodico dei valori di tensione su 8 memorie analogiche, costituite da circuiti di Sample & Hold, per mezzo di un unico DAC a scansione; il contenuto di ciascuno di 8 registri a 12 bit di una RAM viene ciclicamente convertito in una tensione che vie ne campionata dal sample/hold corrispondente e mantenuta fino all'inizio del successivo ciclo di refresh o di aggiornamento.

La velocità massima di variazione della tensione di un dato canale è quindi limitata dalla durata di una scansione attraverso 8 sottoindirizzi (~1 ms); d'altra parte è però consentita una notevole economia di componenti speciali e una compattezza altrimenti difficile da ottenere.

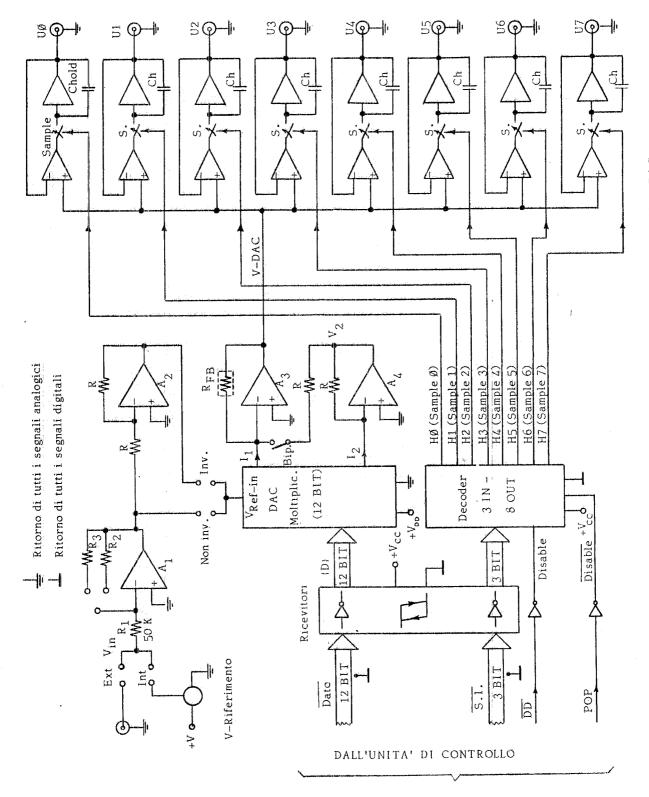

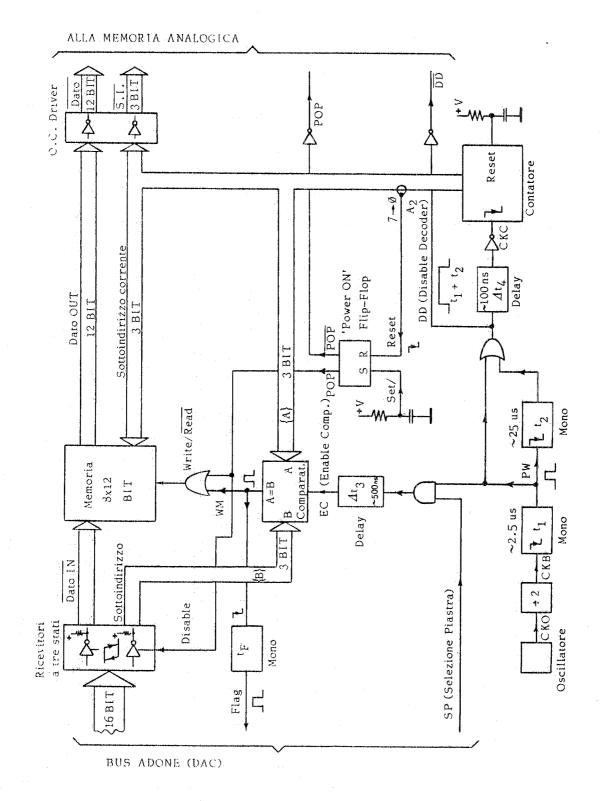

Il MultiDAC è composto da due moduli denominati "memoria analogica" e "unità di controllo". Gli schemi a blocchi dei due moduli sono mostrati nelle Figg. 1 e 2; gli schemi elettrici figurano in Appendice. La piastra di memoria analogica comprende un DAC, gli 8 sample/hold con relativo in dirizzamento e circuiti di condizionamento delle tensioni di ingresso/uscita del DAC. La memoria analogica è contenuta in un modulo standard NIM a singolo spessore, con uscite sul pannello posteriore.

L'unità di controllo comprende il banco di memoria ed i circuiti logici per:

- indirizzamento di lettura/scrittura della memoria;

- sincronismi di controllo e refresh;

- handshake con il calcolatore;

- predisposizione della memoria all'accensione.

L'unità di controllo è contenuta in una carta standard del Bus.

## 3. - FUNZIONAMENTO.

I simboli e le abbreviazioni cui ci si riferisce sono quelli delle Figg. 1 e 2.

#### 3. 1. - Memoria analogica.

La piastra di memoria analogica riceve dall'unità di controllo in modo ciclico un dato di 12 bit e il sottoindirizzo relativo attraverso dei ricevitori invertenti a trigger di Schmidt. Il dato viene convertito in tensione dal DAC, mentre il sottoindirizzo viene decodificato su una di 8 linee che abilitano il trasferimento della tensione del DAC a uno dei canali di uscita (modo sample). Quando il canale non è indirizzato in modo sample la tensione di uscita viene memorizzata (modo hold) in un condensatore ai capi di un buffer con bassa corrente di ingresso (≤ 50 pA) fino al ciclo successivo. Le linee di comando sample vengono inibite per circa 30 μs all'inizio di ciascun intervallo di refresh dal segnale di disabilitazione decodifica, DD, per con sentire l'eventuale aggiornamento dei dati in memoria, la stabilizzazione delle linee digitali e suc

FIG. 1 - Schema a blocchi del modulo "Memoria Analogica" del MultiDAC.

FIG. 2 - Schema a blocchi del modulo "Unità di Controllo" del MultiDAC.

cessivamente la stabilizzazione della tensione di uscita dal DAC e per eliminare l'effetto di glitches sui canali di uscita (vedi Fig. 3). Le linee di comando sample vengono inoltre inibite durante il ciclo di inizializzazione all'accensione.

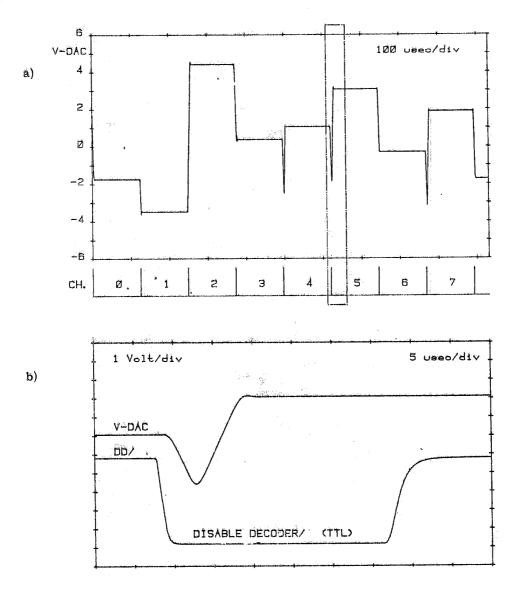

FIG. 3 - Tipica forma d'onda di  $V_{\rm DAC}$ .

a) Variazione di V<sub>DAC</sub> per una scansione completa di 8 canali. Le divisioni in basso indicano il numero del canale. Notare i glitches e gli overshoots/undershoots alle transizioni.

Le forme d'onda di 3a) e 3b) sono state registrate con un voltmetro campionatore HP 3437A e sistema di acquisizione dati HP 3052 A.

b) Visione espansa della zona nel riquadro della Fig. 3a. Il segnale  $\overline{\rm DD}$  disabilità il trasferimento di  $\rm V_{DAC}$  al sample e hold no. 5 per un periodo di tempo ( $\sim 30~\mu s$ ) maggiore della durata del glitch e del tempo di assestamento di  $\rm V_{DAC}$ .

ll DAC utilizzato è un circuito integrato monolitico di tipo moltiplicatore con correnti di uscita quasi complementari  $\rm I_1$  e  $\rm I_2$  date da

$$I_1 = \frac{V_{REF\ IN}}{R_{LD}} \left(\frac{D}{4096}\right) ; \qquad I_2 = \frac{V_{REF\ IN}}{R_{LD}} \left(\frac{4095 - D}{4096}\right)$$

(1)

dove  $R_{LD}$  è la resistenza caratteristica del ladder resistivo interno,  $V_{REF\ IN}$  è la tensione di ingresso al DAC, D è il valore della parola digitale di ingresso (2). La conversione in tensione delle correnti di uscita viene effettuata per mezzo di  $A_3$  e  $A_4$ , che possono essere collegati opzionalmente in modo da ottenere una configurazione di DAC moltiplicatore su due o su quattro quadranti. Nel primo caso si ha:

$$V_{DAC} = -I_1 R_{FB} = -V_{REF IN} \frac{R_{FB}}{R_{LD}} (\frac{D}{4096})$$

$(0 \le D \le 4095)$  (2)

(N.B.:  $R_{FB}$  è integrata nel DAC e ha lo stesso valore e coefficiente termico di  $R_{LD}$ :  $R_{FB}/R_{LD}$  =  $G_{DAC}$  = 1), (mentre nel secondo caso si ha:

$$V_{DAC} = -(I_1 + \frac{V_2}{R})R_{FB} = -(I_1 - I_2)R_{FB} \approx -V_{REFIN} \frac{R_{FB}}{R_{LD}} (\frac{D}{2048} - 1)$$

(3)

$(0 \le D \le 4095)$

(N.B. Sommando una corrente pari a  $V_{\rm REF~IN}/4096$  sulla massa virtuale di  $A_4$ , la(3) è vera senza alcuna approssimazione) in questo caso si dice che il codice applicato è binario con offset (offset = 2048).

Gli amplificatori operazionali  $A_1$  e  $A_2$  servono per il condizionamento di  $V_{\rm REF\ IN}$ . La tensione di ingresso  $V_{\rm in}$  può essere data da un generatore esterno (per esempio, proporziona le all'energia di Adone o del Linac) o da un generatore di precisione interno.  $A_1$  è uno stadio di disaccoppiamento con impedenza di ingresso di 50 k $\Omega$  e guadagno  $G_1$ . Per mezzo di un pon ticello è possibile avere  $G_1$  = -1 o  $G_1$  = -0.5. L'amplificatore  $A_2$  è uno stadio invertitore con guadagno  $G_2$  = -1.

${

m V_{REF~IN}}$  può essere collegata all'una o all'altra delle uscite di  ${

m A_1}$  e  ${

m A_2}$ , cosicchè, in definitiva, il guadagno globale G sarà dato da

$$G = G_1 G_2 G_{DAC} = \begin{cases} 1 \\ 0.5 \end{cases}$$

(4a)

ovvero da

$$G = G_1 G_{DAC} = \begin{cases} -1 \\ -0.5 \end{cases}$$

(4b)

e la tensione di uscita  $V_{\mbox{DAC}}$  sarà:

$$V_{DAC} = -V_{in} G(\frac{D}{4096})$$

unipolare, due quadranti (5a)

$$V_{DAC} = -V_{in} G(\frac{D}{2048} - 1)$$

bipolare, quattro quadranti (5b)

con V<sub>in</sub> tensione di riferimento interna o esterna. Tutte queste possibilità sono selezionabili per mezzo di interruttori DIP (vedi Appendice).

# 3.2. - Unità di controllo.

i) Lettura: Un oscillatore interno forma l'impulso CKC, collegato al clock di un contatore per 8, le cui uscite  $\mathbf{A_0}$ ,  $\mathbf{A_1}$  e  $\mathbf{A_2}$  indirizzano uno di 8 registri a 12 bit del banco di memoria di gitale, normalmente mantenuta in modo "read". Questo processo si ripete indefinitamente in modo ciclico sui sottoindirizzi 0-7; il dato presente al sottoindirizzo corrente e il sottoindirizzo stesso vengono inviati alla memoria analogica per mezzo di drivers invertenti a collettore aperto.

Immediatamente prima delle transizioni da un indirizzo a quello successivo viene formato l'impulso di disabilitazione decodifica, DD, che viene inviato alla memoria analogica per isolare temporaneamente il DAC da tutti i canali di uscita, e durante il quale può avvenire l'aggior namento di un dato in memoria.

ii) Scrittura e handshake: La scrittura di nuovi dati in memoria viene effettuata con la procedura di handshake comunemente impiegata per le altre funzioni del Bus (vedibibl. (1)). Il cal colatore pone sulle linee del Bus dei DAC una parola binaria formata dal valore del dato nei bit 0-11 e dal sottoindirizzo nei bit 12-14. Il segnale di selezione piastra, SP, viene asserito e la parola contenente dato e sottoindirizzo viene mantenuta sulle linee di ingresso fino all'arrivo di uni segnale di Flag, che indica l'avvenuta trascrizione in memoria del dato in questione, al sottoindirizzo indicato.

I ricevitori a tre stati assolvono la duplice funzione di rigenerare le linee del Bus e di forzare le linee di ingresso della memoria a "uno" logico durante il ciclo di inizializzazione.

All'inizio di ogni periodo di refresh viene generato un breve impulso PW della durata di pochi microsecondi, che, in AND logico con SP, dà luogo ad un impulso di abilitazione EC ad un comparatore. Gli ingressi  $\{A\}$  e  $\{B\}$  al comparatore sono rispettivamente il sottoindirizzo corrente e quello specificato dal calcolatore attraverso il Bus. Al verificarsi dell'egua glianza fra  $\{A\}$  e  $\{B\}$  il comparatore genera l'impulso WM di comando scrittura per la memoria e il dato presente sulle linee dei bit  $\emptyset$  - 11 del Bus viene memorizzato al sottoindiriz zo corrente, coincidente con quello specificato. Al termine di WM viene formato un impulso di Flag che segnala al calcolatore l'avvenuta operazione (v. Fig. 4). Il ritardo  $\Delta t_3$  serve ad evitare falsi comandi di scrittura durante le transizioni delle linee  $\{A\}$ .

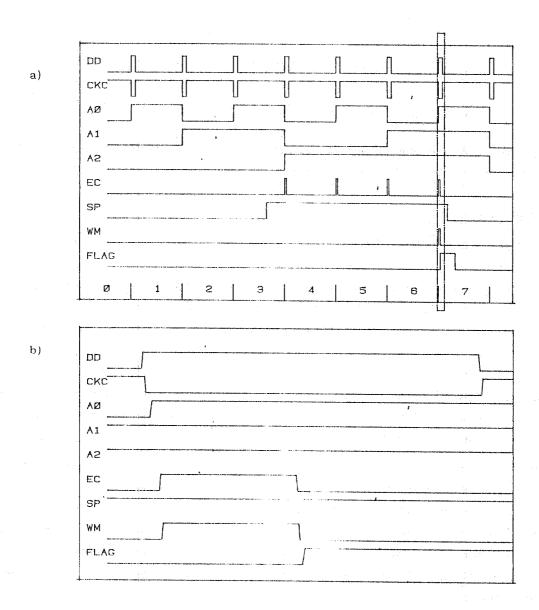

FIG. 4 - Esempio di timing della scrittura di un dato al sottoindirizzo 7.

a) Il calcolatore pone sul Bus dato e sottoindirizzo durante l'indirizzamento del canale 3, asserendo SP; al verificarsi dell'uguaglianza con l'indirizzo corrente viene generato l'impulso WM, il dato viene trascritto in memoria e viene generato un Flag di segnalazione, dopo il quale il calcolatore può disabilitare la piastra.

$\underline{b}$ ) Visione espansa della porzione nel riquadro della Fig. 4a. Notare che il segnale di disabilitazione decodifica DD viene inviato subito prima delle transizioni delle linee di indirizzamento e ha una durata maggiore dell'impulso di comando scrittura WM. Notare anche che l'impulso di abilitazione del comparatore EC avviene dopo che le linee di indirizzamento (in questo caso solo A(0)) si sono stabilizzate, per evitare falsi comandi di scrittura.

iii) Inizializzazione: Il flip-flop di "power on" viene predisposto a uno all'accensione, dando luogo al segnale di power on preset POP, che isola le linee di ingresso al banco di memoria dal Bus e pone la memoria in modo "write". Le linee dei bit \$\infty -10\$ vengono forzate a uno stato di uno lo-

gico, mentre, a scelta per mezzo di un ponticello, il bit più significativo può essere forzato a uno o a zero logico a seconda che si lavori con codice binario puro o con codice binario con offset, rispettivamente.

Le uscite della memoria sono invertite rispetto agli ingressi, cosicchè tutti i datimemo rizzati all'accensione corrispondono a tensione di uscita nulla sugli 8 canali del MultiDAC.

Il flip flop viene azzerato alla transizione 7 → Ø del ciclo di indirizzamento della memoria. Dal momento che il contatore inizia il conteggio da zero all'accensione, è assicurato che tutti i registri siano appropriatamente inizializzati dopo la fase di power on preset.

# 4. - CARATTERISTICHE E PRESTAZIONI.

Sia in fase di progetto che in fase realizzativa si è cercato di minimizzare tutti quei fat tori a discapito delle caratteristiche di precisione, stabilità e linearità associate alla risoluzione nominale di 12 bit (~0.02%).

Si è allo stesso tempo cercato di massimizzare la velocità di risposta compatibilmente con le suddette e con l'architettura generale dell'insieme.

Per i circuiti di condizionamento della tensione di ingresso e del DAC sono state utilizzate reti resistive di precisione a film spesso con rapporto delle tolleranze entro 10 0.02 % e dei coefficienti termici entro  $\pm$  10 ppm/ $^{\circ}$ C e amplificatori operazionali di precisione.

I condensatori dei circuiti di sample/hold sono del tipo con dielettrico a mica per avere resistenza di isolamento elevata e basso adsorbimento del dielettrico.

Il disegno del circuito stampato della memoria analogica ha richiesto una cura particolare per minimizzare il cross-talk fra i canali di uscita e in genere l'effetto di forme d'onda

rapidamente variabili sulle tensioni DC di uscita. Le linee di alimentazione dei circuiti integrati sono generosamente schermate ed i ritorni di tutti i segnali digitali e quelli di tutti i se

gnali analogici sono raggruppati in due linee separate. E' quindi possibile collegare la massa digitale a quella del Bus, che può essere fisicamente distante ed elettricamente rumorosa,

e quella analogica a uno zero Volt "pulito" vicino al punto di utilizzazione.

Sono state eseguite misure di precisione con un sistema di acquisizione dati computeriz zato sui primi esemplari di una piccola produzione di serie, e i risultati sono stati rispondenti alle specifiche di progetto.

Le principali caratteristiche della memoria analogica sono riassunte nella Tabella I.

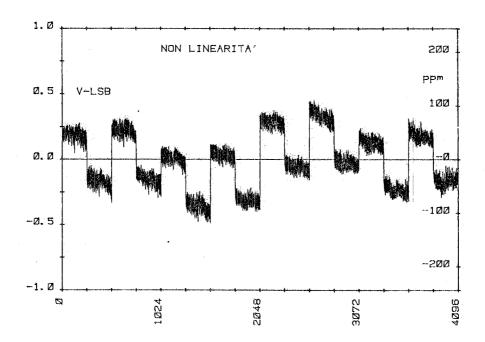

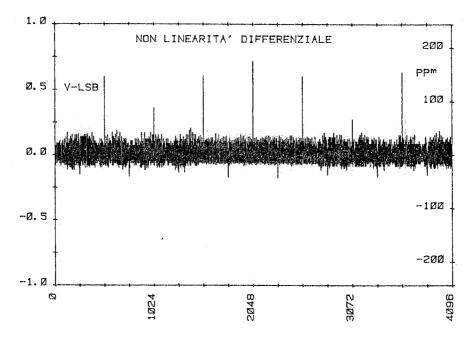

In Fig. 5 è riportato l'andamento tipico della non linearità della tensione di uscita rispetto alla retta ideale, in Fig. 6 è riportato l'andamento della non linearità differenziale.

# TABELLA I - Caratteristiche memoria analogica.

#### Alimentazioni (Standard NIM):

- + 24 V @ 25 mA

- 24 V @ 25 mA

- + 12 V @ 75 mA

## Tensione di riferimento interna:

10.000 V ± 5 mV ± 5 ppm/°C

#### Caratteristiche di trasferimento:

Risoluzione : 12 bit

Guadagno : G =  $\frac{+}{1}$  1.000  $\frac{+}{2}$  0.001  $\frac{+}{2}$  40 ppm/°C  $\frac{+}{2}$   $\frac{16}{\text{Vin}}$   $\frac{\mu\text{V/V}}{\text{°C}}$

G =  $\pm 0.500 \pm 0.001 \pm 50 \text{ ppm/}^{\circ}\text{C} \pm \frac{16}{\text{V}_{in}} \frac{\mu\text{V/V}}{^{\circ}\text{C}}$

Linearità : 12 bit, monotonico

Non linearità rispetto alla retta ideale: - 120 <  $\epsilon_{\rm L}$  < 120 ppm  $\rm V_{FSR}^{(1)}$

(v. Fig. 5)

$-\frac{1}{2} < \epsilon_{\rm L} < \frac{1}{2} \, {\rm V_{LSB}}^{(2)}$

(←L)rms: < 60 ppm V<sub>FSR</sub>

$(\stackrel{\longleftarrow}{\epsilon_L}) \text{ rms} : \stackrel{\longleftarrow}{\epsilon_L} V_{LSB}$

Non linearità differenziale : (v. Fig. 6)

- 60 <  $\epsilon_{\rm D}$  < 180 ppm V $_{\rm FSR}$

$-\frac{1}{4} < \epsilon_{\rm D} < \frac{3}{4} \, \rm V_{LSB}$

(5) rms: <12 ppm V<sub>FSR</sub>

$(\leftarrow_{

m D})$  rms : < 0.05  $\rm V_{LSB}$

Caratteristiche di uscita  $(R_{\tau} > 2 k\Omega)$ :

Stabilità (12 ore) :  $|\Delta V_{OUT}| < 0.1 \text{ mV}$  @  $V_{OUT} = 2.5 \text{ V}$

Non uniformità della tensione di uscita : < 0.02 %

Crosstalk fra i canali di uscita : < -100 db

Ripple nella tensione di uscita : < 1 mV rms

Impedenza di uscita : < 12 $\Omega$  @ | I<sub>OUT</sub>|  $\leq$  5 mA

Slew rate : 0.07  $V/\mu s$

Tempo di aggiornamento : ~ 1 ms

Tempo di refresh :  $\sim$  125  $\mu$ s/canale

Note: (1)  $\mathbf{V}_{FSR} = \left| \mathbf{V}_{OUT} (D=4095) - \mathbf{V}_{OUT} (D=0) \right|$

- (2)  $V_{LSB} = V_{FSR}/4096$

- (3) Quando D è il medesimo per gli 8 canali.

$\overline{\rm FIG.~5}$  - Grafico della non linearità rispetto alla retta ideale,  ${\it E}_{\rm L}$ , in funzione del valore di D, espressa in frazioni di  $\rm V_{LSB}$  e in ppm di  $\rm V_{FSR}$

FIG. 6 - Grafico della non linearità differenziale (definita come  $\epsilon_D$  = [V(D) - V(D - 1)] - V<sub>LSB</sub>; idealmente  $\epsilon_D$  = 0) in funzione del valore di D, espresso in frazioni di V<sub>LSB</sub> e in ppm di V<sub>FSR</sub>. Il valore mas simo si ha alla transizione principale D = 011 \_\_\_111  $\longrightarrow$  1001\_\_000.

#### 5. - CONCLUSIONI.

Il sistema presentato è una soluzione vantaggiosa per l'impostazione da calcolatore di tensioni analogiche non soggette a rapide variazioni nel tempo, come i riferimenti per le famiglie di elementi magnetici di anelli di accumulazione tipo Adone.

Sempre tenendo conto delle esigenze tipiche di Adone è stata consentita una vasta scelta di opzioni di funzionamento in modo da potere avere uscite di ambedue le polarità, proporzionali a riferimenti primari come l'energia della macchina, o assoluti. Le regolazioni iniziali sono agevoli e non richiedono l'interfacciamento con computer, quindi possono essere eseguite su banco; tuttavia, quando non è richiesta la precisione di 12 bit, possono essere omesse.

Il funzionamento è affidabile e si prevede l'installazione di circa 10 di queste unità nell'immediato futuro, nel quadro del lavoro di estensione del sistema di controllo del complesso Adone/Linac per mezzo di calcolatore.

#### RINGRAZIAMENTI,

Desidero ringraziare S. De Simone per la cortese collaborazione offerta e per l'efficien te lavoro di coordinamento della fase realizzativa.

Mi è gradito ringraziare inoltre F. Sanelli per la paziente e puntuale assistenza tecnica prestata durante tutta la realizzazione del progetto e F. Ronci per la attenta esecuzione dei disegni dei circuiti stampati e dei supporti meccanici e per lo scrupoloso lavoro di documentazione.

#### BIBLIOGRAFIA.

- (1) S. De Simone, V. Lauta, M. Matera, C. Ricci, S. Tazzari e G. Vignola, Sistema di acquisi zione dati per la Sala controllo di Adone, Frascati rapporto LNF-73/32 (1973), e Memo Int. Adone SC-78.

- (2) M. Serio, Analisi delle caratteristiche di ingresso-uscita di DAC integrati a Ladder R-2R, Memo Int. Adone SC-105 (1980)

#### APPENDICE

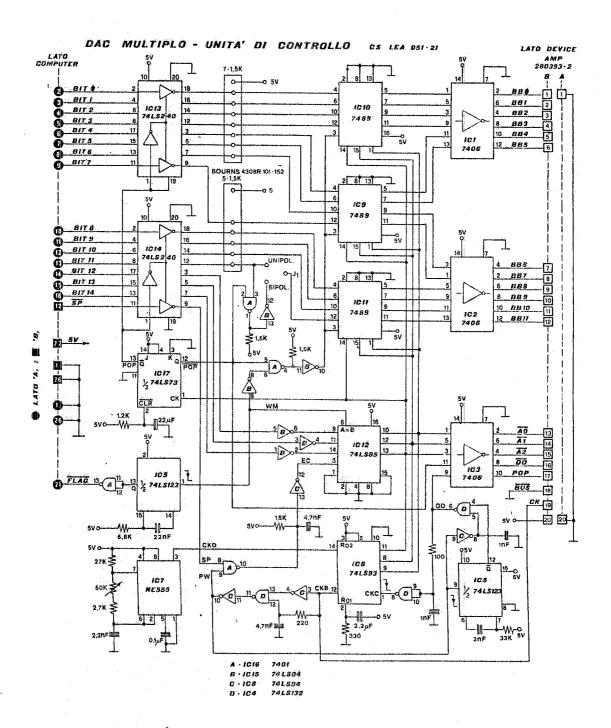

FIG. A1 - Schema elettrico del modulo "Unità di Controllo".

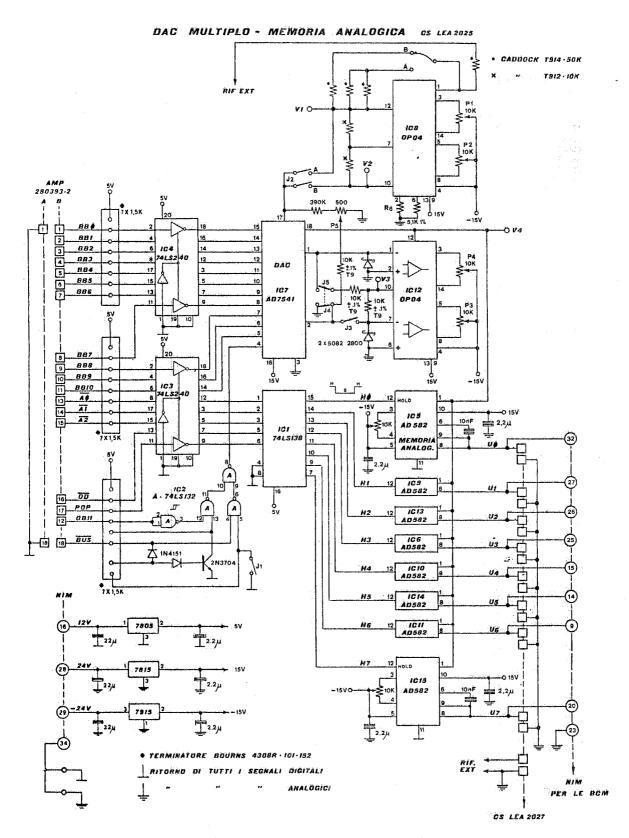

FIG. A2 - Schema elettrico del modulo "Memoria Analogica" nella configurazione con tensione di riferimento esterna.

| RANGE V <sub>OUT</sub> |                                       | J1 <sup>(1)</sup> | J2A <sup>(1)</sup> | J2B <sup>(1)</sup> | J3 <sup>(1)</sup> | J4 <sup>(1)</sup> | <sub>J5</sub> (1)     | JA <sup>(2)</sup> | JB <sup>(2)</sup> | R6 <sup>(3)</sup> |

|------------------------|---------------------------------------|-------------------|--------------------|--------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|-------------------|

| D = 0                  | D = 4095                              | ΩТ                | e ari              | در 4 ن             | சு 3              | <i>ਚ</i> *≭       |                       | υn                | U.D               | 100               |

| Ö                      | V <sub>RIF</sub> (4)                  | ON                | ON                 | OFF                | OFF               | ON                | OFF                   | NO                | SI                | 24. 3             |

| 0                      | - V <sub>RIF</sub> (5)                | ON                | OFF                | ON                 | OFF               | ON                | OFF                   | NO                | SI                | 24.3              |

| - V <sub>RIF</sub>     | V <sub>RIF</sub> (6)                  | OFF               | ON                 | OFF                | ON                | OFF               | ON                    | NO                | sı                | 24. 3             |

| VRIF                   | - V <sub>RIF</sub> (7)                | OFF               | OFF                | ON                 | ОИ                | OFF               | ON                    | NO                | SI                | 24, 3             |

| 0                      | V <sub>RIF</sub> /2 <sup>(8)</sup>    | ON                | ON                 | OFF                | OFF               | ОИ                | OFF                   | SI                | NO                | 16                |

| 0                      | - V <sub>RIF</sub> /2 <sup>(9)</sup>  | ON                | OFF                | ON                 | OFF               | ON                | OFF                   | SI                | NO                | 16                |

| - V <sub>RIF</sub> /2  | <b>1</b>                              |                   | ON                 | OFF                | ON                | OFF               | $\mathbf{ON}_{\perp}$ | ST<br>L           | NO                | 16                |

| V <sub>RIF</sub> /2    | - V <sub>RIF</sub> /2 <sup>(11)</sup> | OFF               | OFF                | ON                 | ON                | OFF               | ON                    | sı                | NO                | 1.6               |

- (1) J1, J2, J3, J4, J5: Interruttori DIP 14 pin

- (2) JA, JB: Ponticelli a saldare

- (3)  $K\Omega \pm 1\% \pm 100 \text{ ppm/°C}$

(4)

$$V_{OUT} = (\frac{D}{4096}) V_{RIF}$$

(5)

$$V_{OUT} = (\frac{D}{4096})(-V_{RIF})$$

(6)

$$V_{OUT} = (\frac{D}{2048} - 1) V_{RIF}$$

(7)

$$v_{OUT} = (\frac{D}{2048} - 1)(-v_{RIF})$$

(8)

$$V_{OUT} = (\frac{D}{4096})(\frac{V_{RIF}}{2})$$

(9)

$$V_{OUT} = (\frac{D}{4096})(-\frac{V_{RIF}}{2})$$

(10)

$$V_{OUT} = (\frac{D}{2048} - 1)(\frac{V_{RIF}}{2})$$

(11)

$$V_{OUT} = (\frac{D}{2048} - 1)(-\frac{V_{RIF}}{2})$$

N.B.  $0 \le D \le 4095$

FIG. A3 - Memoria Analogica.

$\underline{FIG.~A4}$  - Unità di Controllo.