LNF-99/034 (NT) 10 Novembre 1999

# V\_DEV divisore di frequenza programmabile in standard VME 6U

A. Balla, G. Corradi, R. Lenci, G. Paoluzzi, M. Santoni

INFN-Laoratori Nazionali di Frascati, Servizio Elettronica, C.P.13, I–00044 Frascati (Roma) Italia

#### **Abstract**

IL V\_DEV è un modulo divisore in frequenza a 4 canali realizzato in standard VME per ottenere i segnali di campionamento necessari al sistema di acquisizione dell'esperimento NAUTILUS. Il valore della frequenza di uscita può essere impostato singolarmente per ogni canale con una risoluzione di 32 bits. Il modulo accetta segnali in ingresso sia digitali (in standard NIM) che sinusoidali e genera segnali in uscita in standard NIM e TTL.

PACS.: 07.50.E, 84.30 Key words: e.g. PACS

#### 1 - INTRODUZIONE

L'esperimento Nautilus consiste in una barra risonante per la ricerca di onde gravitazionali, la frequenza di risonanza è 1KHz con un Q molto elevato (circa 10<sup>6</sup>). C'è quindi la necessità di avere segnali di campionamento con frequenza 1KHz molto precisa.

Questi segnali sono ottenuti tramite un oscillatore al rubidio che genera un segnale campione (con frequenza 10MHz e una precisione di circa 10<sup>-10</sup>) poi diviso in frequenza.

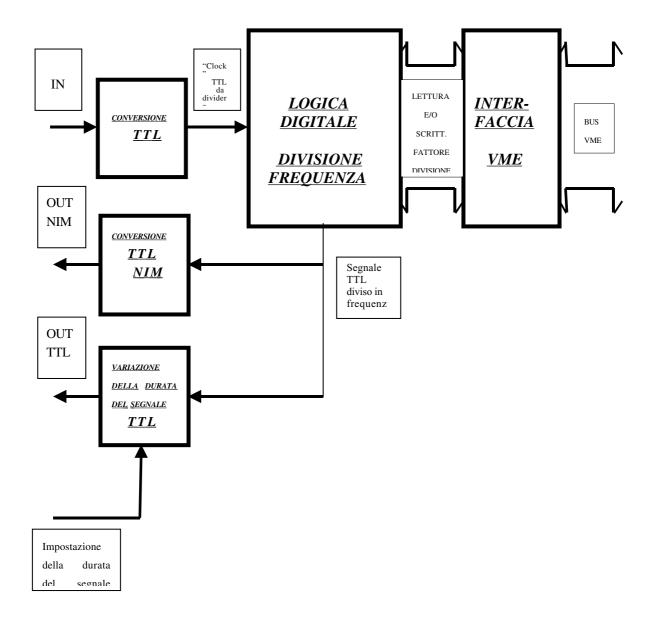

Il modulo V\_DEV è un divisore in frequenza a quattro canali realizzato in standard VME. Il circuito (il cui schema a blocchi è mostrato in fig. 1 ) accetta segnali in ingresso digitali (in standard NIM) o sinusoidali. In quest'ultimo caso la soglia di discriminazione può essere impostata, tramite un trimmer disponibile sul pannello frontale, fra 0 e -2V.

Ogni canale è costituito da un divisore in frequenza a 32 bits ed il segnale in uscita è disponibile sia in standard NIM che TTL; la massima frequenza per i segnali di ingresso è di 50 MHz.

La logica interna del divisore in frequenza è in standard TTL, quindi i segnali in ingresso (in standard NIM o sinusoidali) vengono discriminati da un comparatore a soglia variabile e convertiti in standard TTL prima di essere inviati alla logica di divisione in frequenza.

Per quanto riguarda i segnali disponibili in uscita, il segnale in standard NIM e' un impulso di durata pari al periodo del segnale di ingresso e frequenza fissata dal valore di divisione impostato. Per il segnale TTL è invece possibile fissare la durata del segnale in uscita tramite un trimmer sul pannello frontale (in questo caso la regolazione agisce contemporaneamente sui quattro canali).

L'interfaccia VME è in grado di gestire l'accesso al bus VME secondo lo STANDARD NONPRIVILEGED DATA ACCESS D32 (32bit DATA BUS e 24 bit ADDRESS BUS: AM=39<sub>h</sub>). L'indirizzo del V\_DEV è definito attraverso 3 commutatori e ciascun canale presenta un proprio indirizzo interno (la mappa degli indirizzi è riportata in appendice).

#### 2 - DESCRIZIONE DEL MODULO V\_DEV

I principali blocchi funzionali (vedi fig. 1) che costituiscono il modulo V\_DEV sono:

- a) l'interfaccia VME;

- b) il divisore in frequenza;

- c) lo stadio per l'adattamento dei segnali in ingresso;

- d) lo stadio per l'adattamento dei segnali in uscita;

- e) lo stadio per la regolazione della durata dei segnali TTL in uscita;

di seguito viene fornita una breve descrizione dei suddetti blocchi.

**Figura 1** – Schema a blocchi del mudulo V\_DEV.

## 2.1 – Interfaccia VME

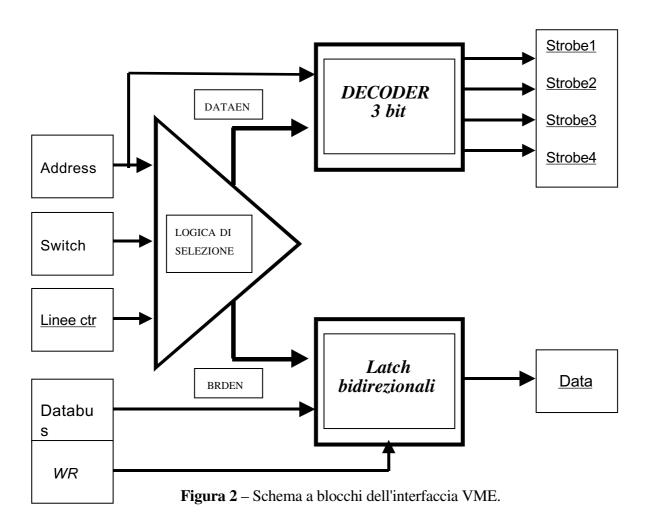

L'interfaccia VME usa il modo di indirizzamento STANDARD NONPRIVILEGED DATA ACCESS D32 (24 bit per il bus degli indirizzi / 32 bit per il bus dei dati) e, da un punto di vista funzionale, può essere suddivisa in tre parti (vedi schema a blocchi di fig. 2)

#### **2.1.1** – *Logica di selezione della scheda*

Questa sezione ha la funzione di verificare se la scheda V\_DEV è stata selezionata, ovvero se il bus VME sta indirizzando la scheda (l'indirizzo della scheda può essere scelto tramite 3 commutatori) e se il bus sta effettuando un corretto ciclo di lettura e/o scrittura (verifica delle linee di controllo). Tale logica genera in uscita due segnali: il primo abilita il decodificatore per la selezione interna del singolo canale mentre il secondo abilita i buffer del data bus.

#### **2.1.2** – Logica di selezione dei canali

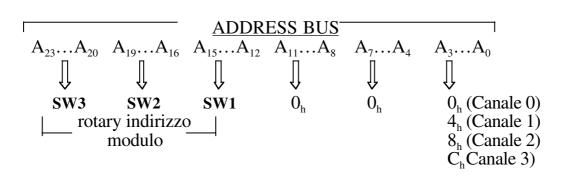

Questa sezione ha la funzione di selezionare uno dei 4 canali interni al V\_DEV; essa è costituita essenzialmente da un decodificatore binario abilitato dal segnale "DATAEN". Il decodificatore ha tre bits di selezione e, a seconda del dato presente sul bus degli indirizzi, seleziona uno dei 4 canali interni al V\_DEV abilitando una delle 4 uscite "STROBE". L'interfaccia, quindi, permette di indirizzare i canali interni del V\_DEV secondo la mappa riportata in fig. 3.

#### **2.1.3** – *Logica di trasmissione dati*

questa sezione è relativa ai buffer del bus dei dati ed è costituita da 4 latch trasparenti bidirezionali abilitati dal segnale "BRDEN". Il trasferimento dei dati è regolato dalla linea WR del VME.

**Figura 3** – Mappa per l'indirizzamento interno al V\_DEV.

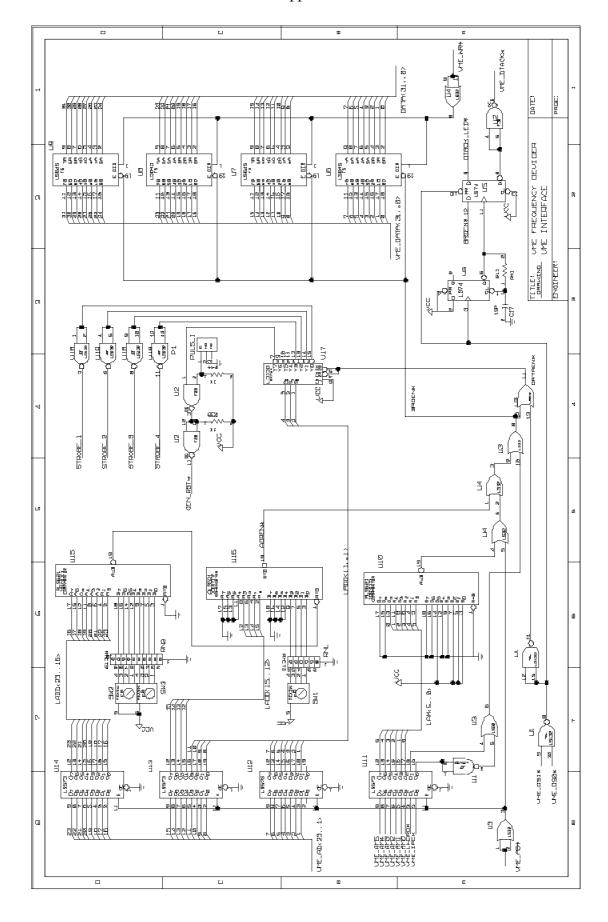

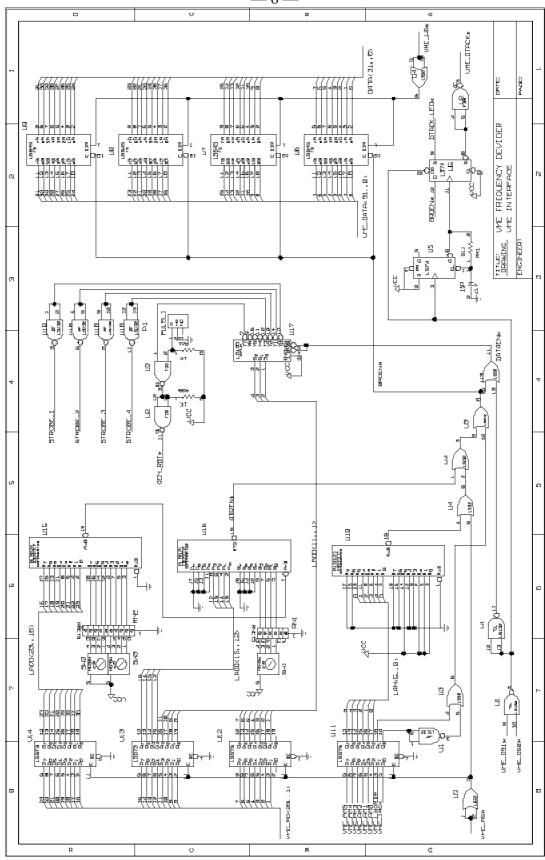

Il circuito elettrico dell'interfaccia e' mostrato in fig. 4.

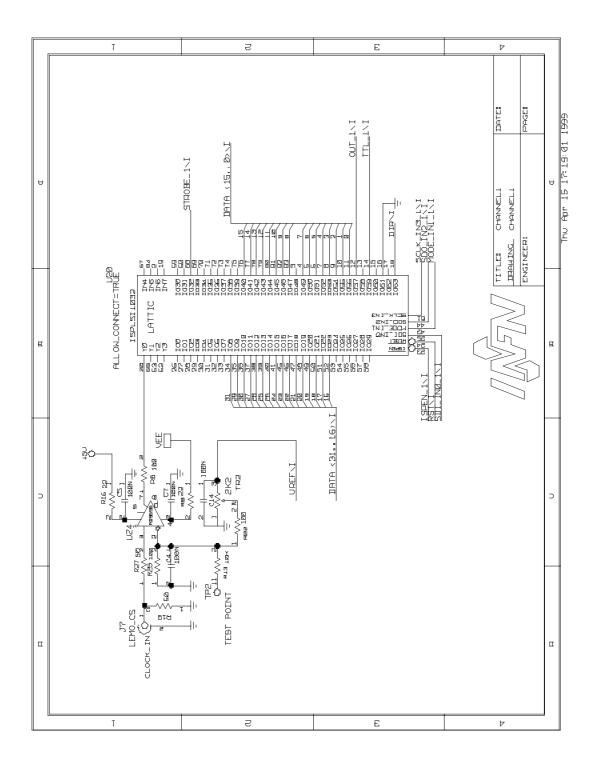

### 2.2 – Logica digitale per la divisione di frequenza

Quattro FPGA ISPLSI1032E della LATTICE sono stati utilizzati per realizzare i quattro divisori in frequenza. Gli ingressi di ogni FPGA sono costituiti da :

- 1) un segnale di abilitazione (STROBE) dal decodificatore a 3 bits,

- 2) un segnale generale di reset,

- 3) 32 bit dall'interfaccia VME per l'impostazione della divisione di frequenza,

- 4) un segnale RW/RD per selezionare le operazioni di scrittura e/o lettura,

- 5) il segnale "CLOCK" da dividere in frequenza.

Il segnale di uscita è unico ed è costituito dal segnale "CLOCK" diviso per il valore impostato. Il circuito logico che effettua la divisione in frequenza è costituito da due divisori a 16 bits; attraverso l'interfaccia VME viene impostata la "parola di divisione" che è legata al fattore di divisione di frequenza (fin/fout) dalla relazione:

*Parola di divisione*= *fin/fout* −*1*

Figura 4 – Circuito elettrico dell'interfaccia VME.

Il segnale in uscita "BORR" è un segnale di periodo pari al periodo del segnale in ingresso moltiplicato per il fattore di divisione impostato e con durata del livello alto pari a un periodo del segnale in ingresso.

La programmazione dei singoli chip è stata effettuata esternamente; all'interno del V\_DEV é stato, comunque, previsto un connettore per la programmazione dei 4 integrati direttamente sulla scheda.

Di seguito sono riportate le equazioni booleane utilizzate per implementare i divisori in frequenza.

#### **2.2.1** – Equazioni dei divisori a 16 bit

```

MODULE devid16

//inputs

clk,ld,rst

pin;

dl15..dl0

pin;

//output

borr pin istype 'com';

q15..q0 node istype 'pos,reg,buffer';

declarations

data = [dl15..dl0];

counta = [q15..q0];

equations

counta := !ld & (counta - 1)

# ld & data;

counta.ar = rst;

counta.clk = clk;

borr = (counta == 0);

END

```

#### 2.3 – Stadio di adattamento dei segnali in ingresso

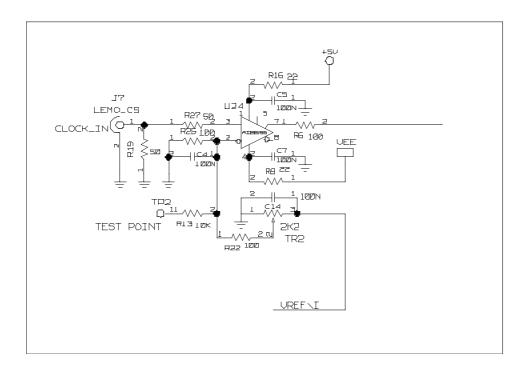

Come si è detto, il V\_DEV è in grado di accettare segnali in ingresso sia digitali (in standard NIM) sia sinusoidali. Lo stadio di ingresso è, infatti, costituito da un comparatore con un campo di regolazione della soglia compreso tra 0 e -2V (il valore impostato può essere controllato esternamente tramite un test point disponibile sul pannello frontale). Lo schema elettrico dello stadio d'ingresso è riportato in fig. 5.

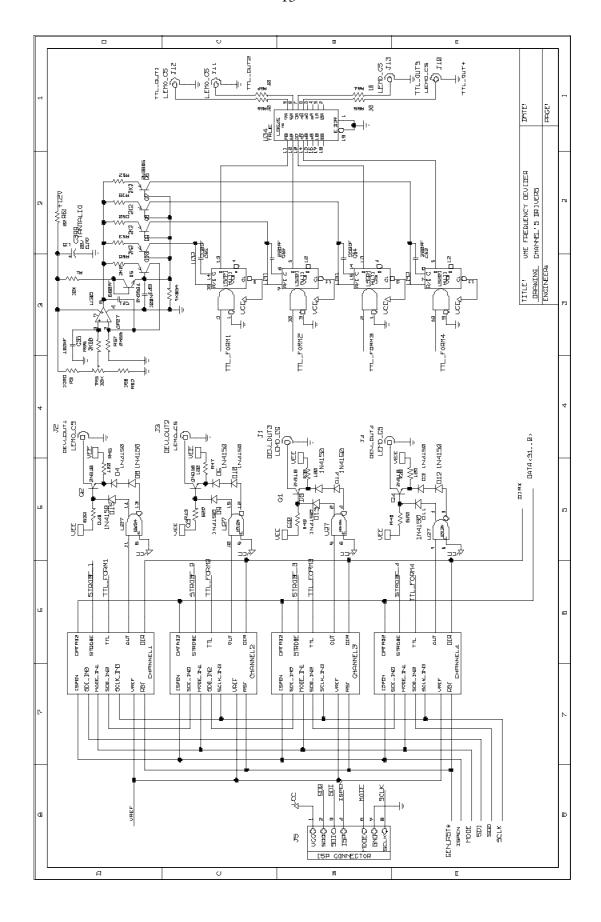

**Figura 5** – Stadio di adattamento dei segnali in ingresso.

# 2.4 - Stadio di adattamento dei segnali di uscita

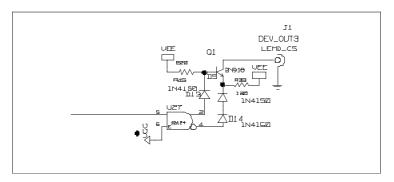

I segnali "BORR" che escono dagli integrati LATTICE nello standard TTL (0V / +5V) vengono convertiti nello standard NIM (0V / -0.8V) utilizzando il circuito riportato in figura 6.

Figura 6 – Stadio di adattamento dei segnali in uscita.

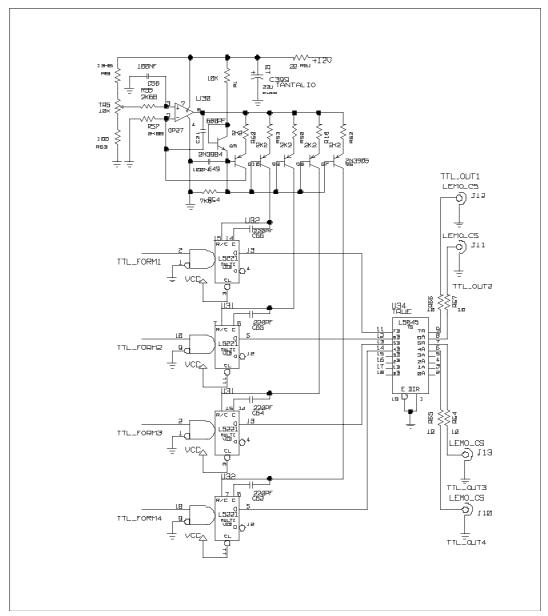

#### 2.4 – Stadio per la regolazione della durata dei segnali TTL in uscita

Lo stadio di uscita dei segnali TTL (vedi fig. 7) è composto da 4 monostabili. I monostabili sono pilotati da un generatore di corrente variabile a 4 uscite; agendo sul trimmer presente sul pannello frontale del modulo si varia la corrente in uscita del generatore che, caricando più o meno velocemente la capacità esterna del monostabile, varia la durata del segnale di uscita. I valori del generatore di corrente e delle capacità dei monostabili sono stati calcolati per permettere un campo di variazione nella durata del segnale in uscita compresa tra un minimo di 250 ns ed un massimo di 1µs.

Figura 7 – Stadio per la regolazione della durata dei segnali TTL in uscita.

# 3 – APPENDICE

# 3.1 - Specifiche del modulo V\_DEV

Impedenza di ingresso: 50 ohmSoglia segnali di ingresso: 0/-2vFrequenza massima in ingresso: 50 MhzImpedenza di uscita (uscite NIM): 50 ohmDurata del segnale di uscita (TTL): 250ns-1us

# 3.2 - Tabella di conversione commutatori/bus degli indirizzi

| Commutatore | Bus degli indirizzi |

|-------------|---------------------|

| 0           | 0                   |

| 1           | 8                   |

| 2           | 4                   |

| 3           | С                   |

| 4           | 2                   |

| 5           | A                   |

| 6           | 6                   |

| 7           | Е                   |

| 8           | 1                   |

| 9           | 9                   |

| A           | 5                   |

| В           | D                   |

| С           | 3                   |

| D           | В                   |

| Е           | 7                   |

| F           | F                   |

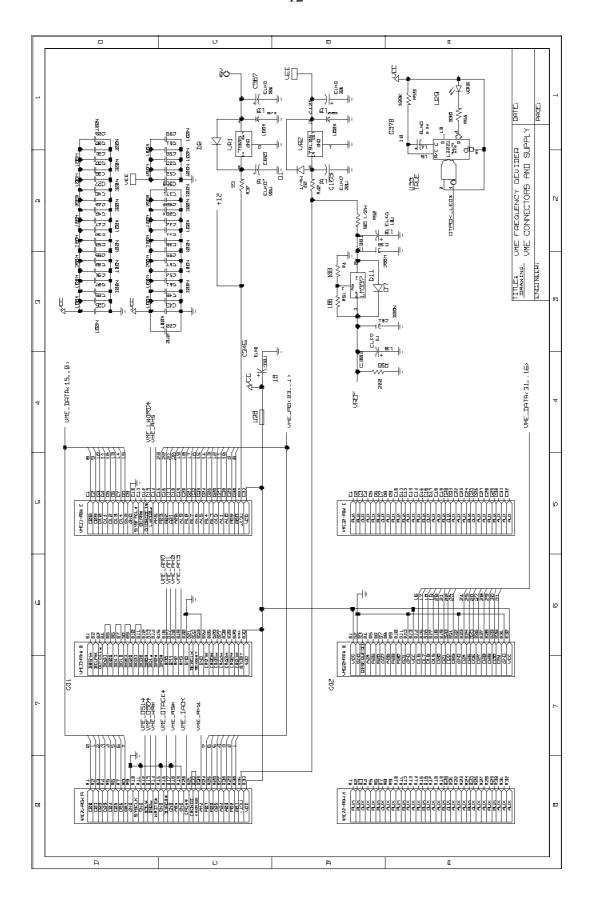

## 3.3 – Schemi elettrici

Nelle pagine seguenti sono riportati gli schemi elettrici completi del modulo V\_DEV.