# ISTITUTO NAZIONALE DI FISICA NUCLEARE

Sezione di Genova

INFN/TC-98/14 16 Giugno 1998

M. Olcese, S. Farinon:

ATLAS PIXEL DETECTOR BUMP BONDING STRESS ANALYSIS

# <u>INFN – Istituto Nazionale di Fisica Nucleare</u> Sezione di Genova

INFN/TC-98/14 16 Giugno 1998

# ATLAS PIXEL DETECTOR BUMP BONDING STRESS ANALYSIS

M. Olcese, S. Farinon

INFN – Sezione di Genova, via Dodecaneso 33, I-16146 Genova (Italy)

#### Abstract

In order to route the output signals from the ATLAS pixel detector to the read-out integrated chips, the bump bonding technology will be used. The design should be quite aggressive as high connection density (4000 connections in  $0.8~\rm cm^2$ ) and very small bump dimensions (20  $\mu m$   $\Phi$  are required). Since it is critical to keep the detector efficiency high, the probability of breaking bumps during construction, installation, operation and maintenance must be minimised. To help reaching that aim, a preliminary analysis has been performed in order to evaluate the stress applied on the bump bondings, as function of the expected loads, the thermal one being the most significative.

### 1. INTRODUCTION

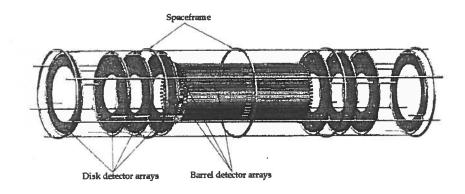

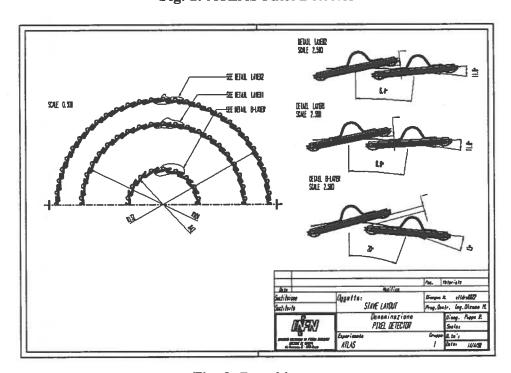

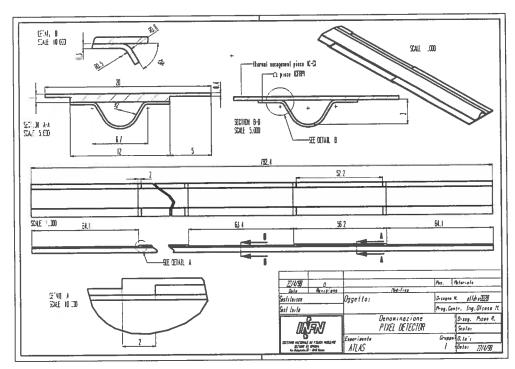

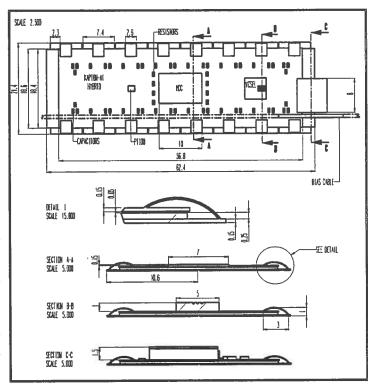

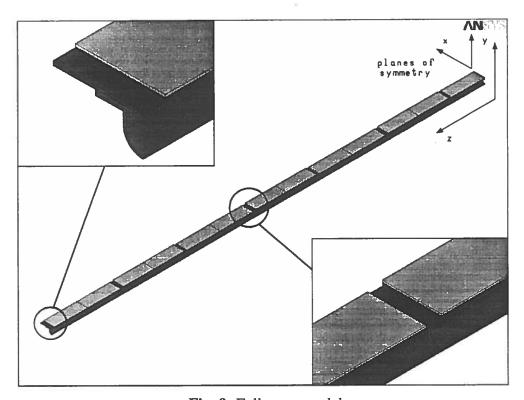

The ATLAS pixel detector system (Fig. 1) provides critical tracking information for pattern recognition near the collision point [1]. It is composed of modular units. Read out integrated circuits are mounted on a detector substrate made of silicon to form barrel and disk modules, using bump bonding techniques. The barrel modules (Fig. 2) are mounted on supporting structures, the staves, that are also identical throughout the system (Fig. 3 shows the stave design made by INFN-Genova, taken as reference for this analysis). The resulting mechanical structure must be very stable and provide the cooling capability to maintain the silicon temperature  $\leq$  -6 °C, even with the large heat load from the electronics and other sources.

Fig. 1: ATLAS Pixel Detector

Fig. 2: Barrel layout

Fig. 3: Stave assembly

# 2. ATLAS PIXEL DETECTOR: BUMP BONDING TECHNOLOGY

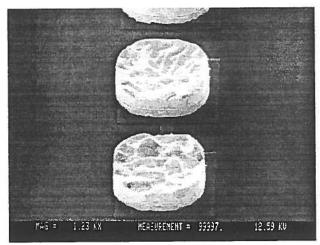

Bump bonding and flip chip assembly are critical elements of the module assembly process. Each module is made of 16 electronic chips bump bonded on the silicon detector substrate. The bump creation process involves deposition of indium or tin-lead materials on the

integrated circuits and detectors, to form a small bump, typically 20 µm in diameter and 15 µm in height. Bump deposition is made either via an evaporating process or via processes. After electrochemical deposition, the wafers are diced and joined by flip chip assembly, accomplished by precise optical alignment. Finally pressure or heating cycles are applied to solder the bumps. The bump bonding technology used in ATLAS is quite aggressive due to the high density and the small dimensions of bumps, which have a diameter 10 times smaller than the bumps produced by well-established industrial processes.

Fig. 4: 20  $\mu$ m  $\Phi$ , 50  $\mu$ m pitch Indium bumps

#### 3. CALCULATION APPROACH

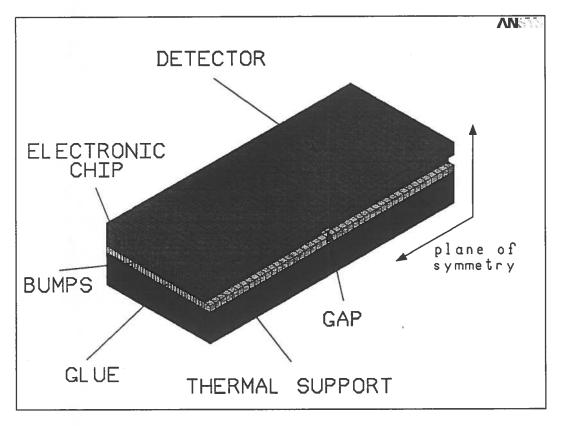

Two types of modules are under investigation. The configuration (Fig. 5) which minimise the amount of material and the insulation problems between the detector and the support structure is the one based on a conventional flexible hybrid with wire bond

connections from the front end chips to the power and signal bus of the hybrid. In this configuration the mounted with module is the electronic chips attached to the mechanical support structure. This is the chip down module type and we have considered this design in the present study. In the chip-down configuration the electronic chips can have relative displacements, since they are not bonded one each other. Therefore the relative displacement between the stave and the detector to the thermal expansion coefficient (CTE) mismatch induces a stress on the bumps. In order to evaluate the amount of stress on bumps and to check if the allowable limits are exceeded, a detailed simulation of a stave has been performed, using the ANSYS finite element analysis code [2].

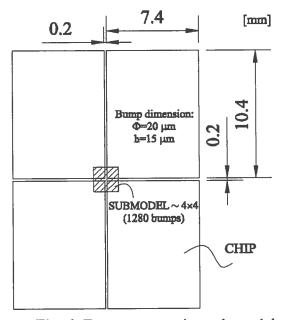

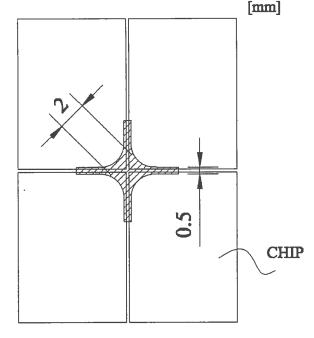

Since a full stave model with bumps is completely out of FEA computer capability, due the very small size of the bumps (20  $\mu$ m in diameter and 15  $\mu$ m in height), a submodelling approach has been used (see Fig. 6). Therefore the analysis has been split into three steps:

- A sensitivity study on a small model with the real geometry (bump modelled) has been performed to find out a simplified configuration equivalent in term of displacements to the real one.

- A full model, as result of the previous step, has been then analysed, identifying the maximum strain region where the maximum value of stress on bump is expected.

Fig. 5: Module layout

Fig. 6: Four corner region sub-model

• The results (displacements) of the full stave analysis have been finally applied as boundary conditions to a local sub-model and the stresses on bumps have been evaluated.

#### 4. GLUE BONDING SENSITIVITY STUDY

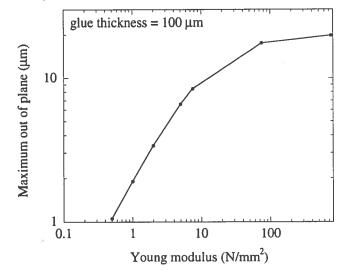

The module is mechanically coupled to the stave by mean of a thin layer of glue. The stave

bowing, the sensor deflection and stress on bumps, due to the stave-sensor CTE mismatch, all depend on the rigidity of the glue layer. A sensitivity study of the influence of the glue elasticity on the sensor deflection has been done using a simplified model of one module attached to a stave 7 plots the maximum portion. Fig. displacement induced on the sensor as function of the glue Young modulus; it can be observed that only a very low Young modulus (typical of greases) leads to a significant reduction of the displacements. That is the reason why a grease instead of a glue will be probably used, to minimise the influence of the temperature gradients on the stave stability.

Fig. 7: Pixel sensor deflection sensitivity study

#### 5. SMALL SCALE SENSITIVITY ANALYSIS

The bumps with higher stress are located near the electronic chip edges; therefore the small scale model has been built around the four corner region of the electronic chips (see Fig. 6). The model is shown in Fig. 8 and includes 1280 bumps, simulated as beam elements (ANSYS element BEAM4). The material properties used in the simulation are listed in Table I; due to their very small dimensions, the CTE of bumps has been neglected. All materials have been assumed to have elastic behaviour.

The ATLAS collaboration is currently studying two different bump materials: tin-lead alloy and indium, both materials have been taken into account.

| Material            | Young modulus (MPa) | CTE (10 <sup>-6</sup> K <sup>-1</sup> ) | Yield stress (MPa) |

|---------------------|---------------------|-----------------------------------------|--------------------|

| Silicon             | 131000              | 2.3                                     |                    |

| Glue                | 7.5÷7500            | 30                                      | _                  |

| C-C (2D) in plane   | 185000              | -1                                      | _                  |

| C-C (2D) transverse | 50000               | 6                                       |                    |

| Indium bump         | 10600               | _                                       | 2.6÷4.5            |

| Sn-Pb bump          | 26000               | <del>_</del>                            | 52                 |

Table I: Small scale model material properties

Since the full stave model can not take into account the bumps and the discontinuity between electronic chips, the purpose of the sensitivity study is to find out in which conditions a simplified model is equivalent to the real one. The equivalence has been checked in terms of displacements, since the stress on bumps will be evaluated applying as boundary conditions to the small scale model with the real geometry the displacements coming from the full stave simplified analysis.

The simplified model consists of the real model where both the gaps between the electronic chips and the gap between the sensor and the electronic chips are filled with silicon.

The results of the sensitivity analysis are summarised in Table II; it can be observed that the simplified model and the real one are equivalent only at low Young modulus values. Since the more probable candidate as bonding medium is a grease, with a Young modulus much lower than 7.5 MPa, this value has been adopted as reference to perform the analysis.

| Young modulus (MPa) | Real geometry max displacement (10 <sup>-7</sup> m) | Simplified model max displacement (10 <sup>-7</sup> m) |

|---------------------|-----------------------------------------------------|--------------------------------------------------------|

| 7.5                 | 2.4                                                 | 2.4                                                    |

| 7500                | 3.8                                                 | 2.2                                                    |

Table II: Sensitivity analysis results

Fig. 8: Small scale model (real geometry)

#### 6. FULL STAVE ANALYSIS

As results of the sensitivity analysis, a full stave model neglecting the bumps and the discontinuity between the electronic chips has been studied (see Fig. 9). The model (3·10<sup>4</sup> nodes) simulates in details all the mechanical interfaces between the module and the C-C support and between the C-C support and the omega carbon fibre composite channel (see Fig. 3). The omega piece is made of three layers of carbon fibre composite with 0°/90°/0° stacking sequence; each layer is made of M60J unidirectional fibres plus 954-2A Fiberite cyanate-ester resin.

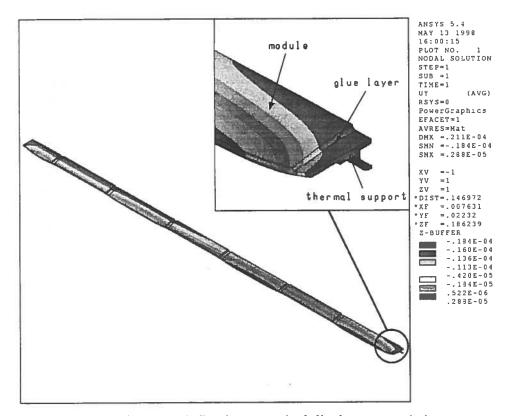

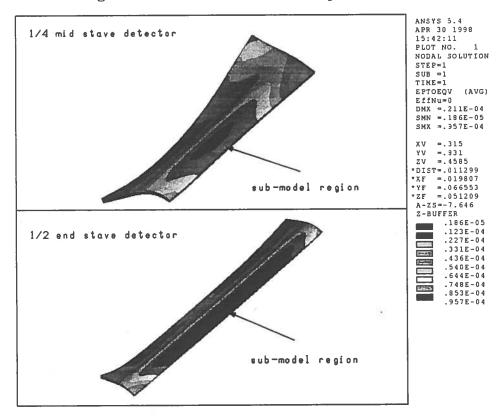

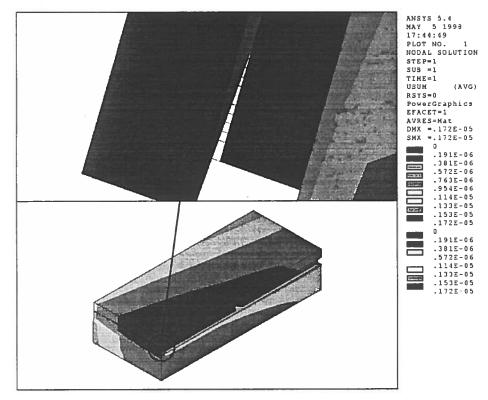

The stave has been assumed to be simply supported at the two ends and the mid point. The stave deflections, induced by the weight of the stave and the CTE mismatch between the different material used, have been evaluated (see Fig. 10). Two maximum strain regions on silicon have been identified (see Fig. 11): one at each stave end and the other in the middle of the stave. The results (displacements) of this analysis have been finally applied as boundary conditions to a local sub-model (see Fig. 8) and the stresses on bumps have been evaluated.

Fig. 9: Full stave model

Fig. 10: Stave deflections: vertical displacements (m)

Fig. 11: Maximum strains on silicon

#### 7. BUMP STRESS ANALYSIS

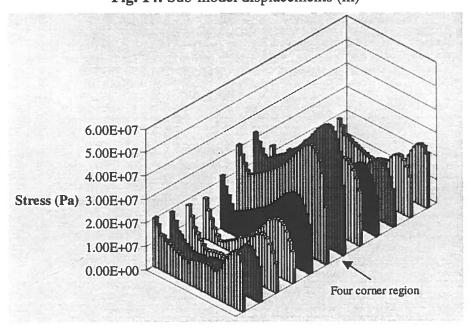

The maximum stresses on bumps occur both on the two end modules and the mid one. As expected the maximum stressed bumps are located exactly all around the four corner region. The maximum stresses, evaluated with reference to a glue with a Young modulus of 7.5 MPa, are summarised in Table III as function of the bump material and compared with the yield stress. The maximum stresses do not depend on the sub-model locations (mid or end module). The model displacements and the distribution of the stress within bumps are

materials:

just

for

reference

qualitatively the same for both bump displacements and the stress on bumps are plotted respectively in Fig. 14 and Fig. 15 for

SnPb bumps.

Table III: Maximum stresses on bumps

|                         | SnPb<br>bumps | In<br>bumps |

|-------------------------|---------------|-------------|

| Maximum stress<br>(MPa) | 52            | 35          |

| Yield stress (MPa)      | 50            | 2.6÷4.5     |

Both in case of SnPb and In bumps the yield stress is reached, but while for SnPb bumps the plasticity region extends just over few bumps (~5), for In bumps the plasticity region (shown in Fig. 12) includes roughly 150 bumps. Anyway also for In bumps the extent of the plasticity region is limited to few mm<sup>2</sup> centred in the four corner region.

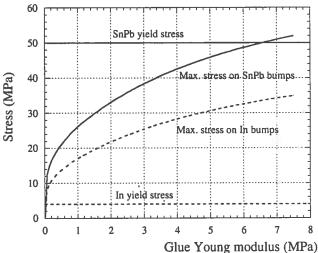

As result of these first calculations, performed with reference to a glue with a Young modulus of 7.5 MPa, the analysis has been extended to evaluate the effects of a further increase of the glue elasticity (lower Young modulus values) on the maximum stress on bumps. The results are plotted in Fig. 13. While for the SnPb bumps a safety factor of two with respect to the yield stress is reached for glue Young modulus lower than 1 MPa, very low glue Young modulus values are required to avoid that the yield stress within In bumps is reached.

Fig. 12: Plasticity region: In bump case

**Fig. 13:** Maximum stress on bumps vs. glue Young modulus

Anyway the portion of the curve plotted in Fig. 13 at very low glue Young modulus is difficult to be explored, since the model adopted for this analysis fails. Therefore the results plotted for this region, in particular for In bump case, have to be considered only as reference. Due to the complexity and the criticality of the problem, only an experimental investigation can deeply explore the behaviour of the system when a grease is used as bonding medium.

Fig. 14: Sub-model displacements (m)

Fig. 15: Stress on bumps; same perspective view as Fig. 8

# 8. CONCLUSIONS

A first analysis of the stress on bumps, due to the stave operating conditions and performed with reference to the INFN-Genova stave design, leads to the following conclusions:

- The maximum stresses on bumps occur on the modules located at the three support constraints (two ends and mid stave) in the four corner region.

- For SnPb bumps a safety factor of two can be easily obtained with a glue Young modulus lower than 1 MPa.

- For In bumps this analysis gives only qualitative results: a very low Young modulus glue (<<1 MPa) must be used to ensure that the yield stress is not exceeded; the extent of the plasticity region is limited to few mm² all around the four corner region. Since indium is a very plastic material, which can largely deform before breaking, the fact that the yield stress is reached within bumps does not mean that a break occurs. Furthermore the expected numbers of thermal cycles during operation is very limited so that the fatigue phenomenon should not be critical.

Anyway only an experimental approach can validate the results of this analysis, particularly if In bumps should be used.

#### REFERENCES

- [1] ATLAS INNER DETECTOR TECHNICAL DESIGN REPORT, ATLAS TDR 5, CERN/LHCC/97-17, 30 April 1997.

- [2] ANSYS<sup>®</sup>, Revision 5.4, Swanson Analysis Systems, Inc.