# ISTITUTO NAZIONALE DI FISICA NUCLEARE

Sezione di Bari

$\frac{\mathrm{INFN/TC-82/5}}{\mathrm{19~Aprile~1982}}$

P. Tempesta e A. Valentini: SISTEMA DI ACQUISIZIONE DATI MULTIPARAMETRICO CON INTERFACCIA DR11-C VERSO UN PDP 11/34.

> Servizio Documentazione dei Laboratori Nazionali di Frascati

Istituto Nazionale di Fisica Nucleare Sezione di Bari

> INFN/TC-82/5 19 Aprile 1982

SISTEMA DI ACQUISIZIONE DATI MULTIPARAMETRICO CON INTERFACCIA DR11-C VERSO UN PDP11/34.

P. Tempesta INFN, Sezione di Bari

A. Valentini Istituto di Fisica dell'Università di Bari

#### INTRODUZIONE.

L'uso di sistemi di acquisizione dati a più parametri dipendenti è divenuto una necessità sempre crescente anche in esperimenti di Fisica Nucleare delle Basse Energie.

Le motivazioni sono da ricercarsi nell'impiego di tecniche sempre più sofisticate per identificare carica, massa, tempi, coordinate posizionali, energia, stopping power, ecc., spesso contemporaneamente, con l'indubbio vantaggio di acquisire una rilevante parte dello spazio delle fasi relativo ai detti parametri, riservando al playback dell'esperimento la scel ta opportuna di finestre per selezionarli.

Di un sistema acquisizione dati multiparametrico molte parti possono trovare una vasta gamma di soluzioni tecniche commerciali quali il mini computer, l'interfaccia per la trasmissione parallela di una o più parole, il convertitore analogico digitale (ADC).

Il limite più serio che proviene alla rapidità di acquisizione dati di un sistema multiparametrico è la relativa lentezza operativa degli ADC in commercio con elevato numero di bit

e buona precisione. Se si sceglie tuttavia, per vari motivi, di adoperarli per un sistema multi

parametrico, è quasi impossibile accontentarsi della lentezza intrinseca che proviene dall'uso

di stretchers e conversioni successive. Ci si orienta allora su batterie di convertitori in paral lelo con un interfaccia che governa la trasmissione successiva dei dati convertiti. In questo mo do si realizza l'acquisizione multipla con un incremento soltanto del 10% - 20% del tempo di conversione di un singolo ADC.

Nei successivi paragrafi vengono descritti due sistemi di acquisizione dati a quattro para metri realizzati presso il Gruppo di Fisica del Nucleo di Bari.

## 1. - ELETTRONICA DI TRASMISSIONE.

La scelta di convertitori in parallelo pone come problema conseguente quello della scelta dell'interfaccia per l'acquisizione dei dati al calcolatore. Inoltre, se si tiene conto che il siste ma di acquisizione prevede che i quattro ADC convertano da uno stesso evento quattro parame tri diversi, e quindi presentino i loro dati "contemporaneamente", oppure convertano ciascuno un evento diverso presentando i loro dati in forma "random", risulta altresì chiaro che la scel ta di un interfaccia dedicata diventa difficoltosa nonchè onerosa.

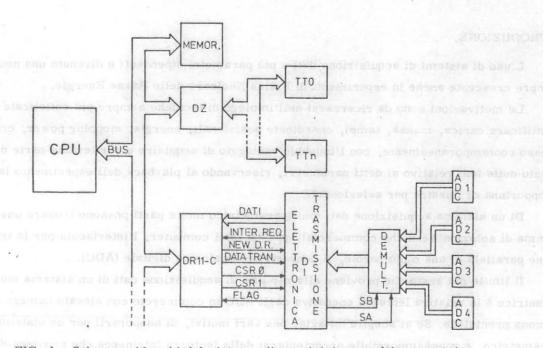

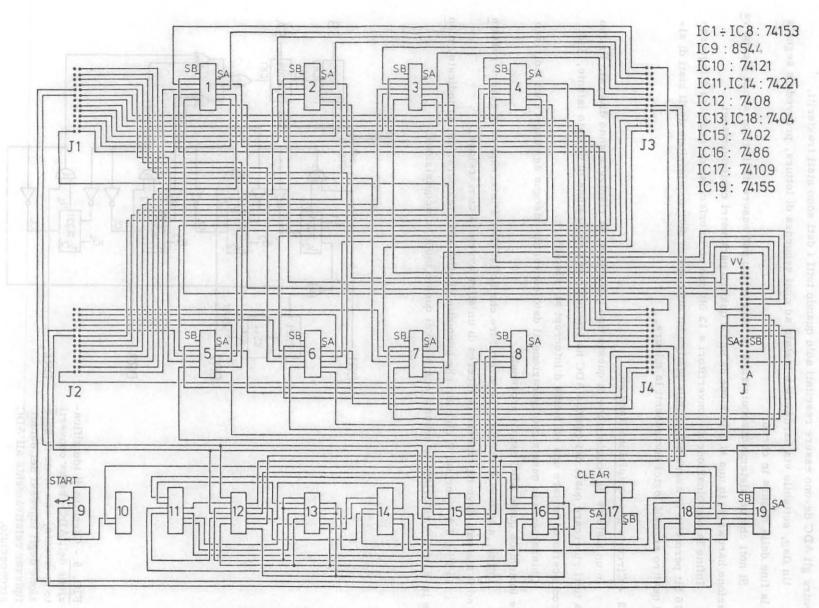

Pertanto ci si è indirizzati ad un'interfaccia del tipo general purpose e si è integrato il sistema di acquisizione dati (Fig. 1) con una parte di elettronica da noi progettata e realizzata.

E' stata scelta un'interfaccia Digital da montare su bus di mini computer PDP 11/34 e precisamente una DR11-C le cui proprietà basilari sono quelle di poter essere gestita ad interrupt hardware, nonchè di possedere due soli registri dati a 16 bit ciascuno, uno di input e l'al tro di output.

La parte di conversione viene effettuata tramite quattro ADC Silena 7411/N a 12 bit.

FIG. 1 - Schema a blocchi del sistema di acquisizione multiparametrico.

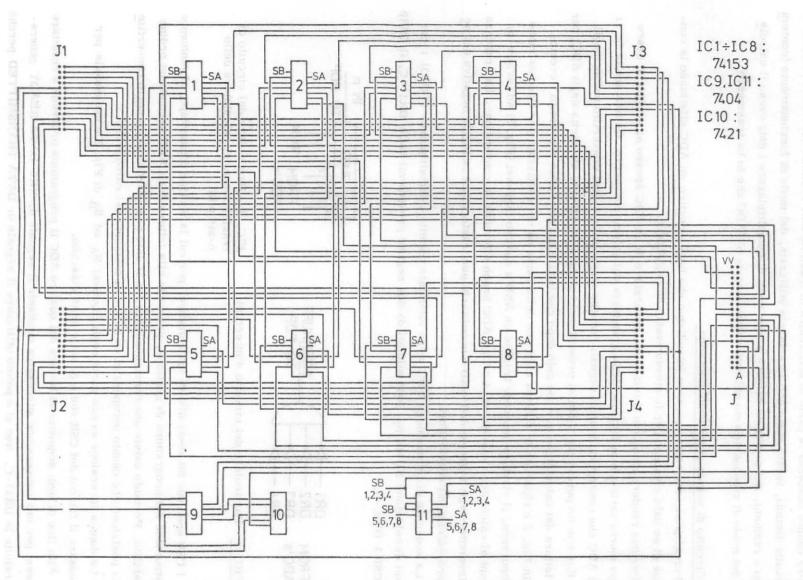

$\underline{FIG. 2}$  - Schema elettrico del circuito di acquisizione contemporanea. Il connettore J collega il circuito con la DR11-C. I connettori Jn lo collegano al relativo convertitore.

Per quanto concerne la parte di elettronica di trasmissione restante sono stati realizzati due circuiti distinti, tenuto conto dell'interfaccia utilizzata, del modo di funzionamento (contemporaneo o random), del problema comune ai due modi di demultiplexare i dati verso il calcolatore e del modo di riconoscimento del dato relativamente all'ADC che lo ha trasmesso.

## 1.1. - Circuito di acquisizione contemporanea.

Per acquisizione contemporanea intendiamo che tutti e quattro gli ADC effettuano la conversione di un dato ciascuno per lo stesso evento da registrare.

Per non rendere massimo il tempo di conversione di un ADC spesso si sceglie di usare il tempo morto variabile in funzione della grandezza del valore convertito. Questa scelta fa si che gli ADC che convertono piccoli segnali rendono disponibile il dato convertito prima degli altri. Non è detto perciò che i dati si presentino contemporaneamente all'uscita degli ADC, per cui la lettura dal calcolatore avviene solo dopo che tutti e quattro hanno convertito l'evento.

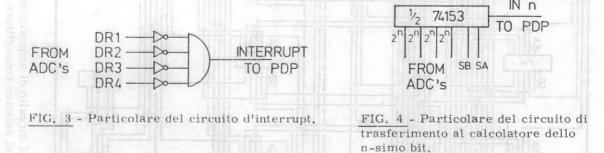

In Fig. 2 è riportato lo schema elettrico della parte da noi realizzata per l'acquisizione contemporanea. Il circuito provvede tramite un AND a quattro ingressi (Fig. 3) ad inviare un interrupt al calcolatore solo quando tutti gli ADC hanno effettuato la conversione. La presenza degli invertitori agli ingressi dell'AND è necessaria per trasformare la logica negativa dei se gnali provenienti dai convertitori.

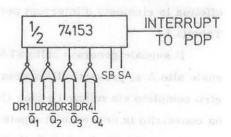

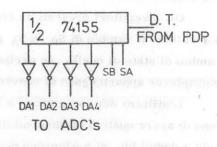

La sequenza di lettura degli ADC viene effettuata tramita i demultiplexer (74153) i cui ingressi di selezione  $S_A$  ed  $S_B$  sono pilotati da due segnali provenienti dalla DR11-C, il CSR $\phi$  ed il CSR 1 (Fig. 4).

I CSR sono due bit controllabili via software, per cui la routine d'interrupt, al momento di costruzione del programma di gestione, provvede alla lettura degli ADC secondo un ordine prestabilito. Pertanto esiste una corrispondenza fra il dato proveniente da un certo convertito re e la posizione che questo occuperà in un buffer di memoria del calcolatore.

La doppia inversione su una parte degli ingressi  $S_A$  ed  $S_B$  di Fig. 2 è necessaria per compensare il fan out dei CSR che è di sette unità ciascuno.

Alla fine di ogni sequenza di lettura dei quattro ADC il programma provvede a resettare gli stessi per una conversione successiva mediante il segnale di NEW DATA READY generabile tramite la DR11-C. Non si è potuto utilizzare il segnale di DATA TRANSMITTED perchè questo viene generato dalla DR11-C ogni qualvolta si presenta un dato al registro di ingresso,

mentre gli ADC devono essere resettati solo quando tutti i dati sono stati trasferiti.

Un flag, settabile via hardware e testato ad ogni sequenza di lettura, provvede a segnalare la fine della misura in corso.

Si noti che un sistema di acquisizione di questo tipo può essere utilizzato, senza alcuna va riazione hardware, in una acquisizione da uno a quattro parametri contemporanei.

Infine la combinazione di convertitori a 12 bit con un'interfaccia con registro d'ingresso a 16 bit permette di avere disponibili quattro bit utili ai fini dell'acquisizione degli stati di altri quattro segnali logici componenti la misura.

## 1.2. - Circuito di acquisizione Random.

In un sistema di acquisizione di questo tipo i problemi da risolvere sono diversi. Primo fra tutti ricercare quale dei quattro ADC ha effettuato la conversione in un dato istante, indi riconoscerlo ed inviare una richiesta d'interrupt al calcolatore.

Chiaramente in questa configurazione al dato convertito bisogna aggiungere un indirizzo che indichi da quale ADC esso è provenuto.

Infine, a lettura avvenuta, il convertitore che ha lanciato l'interrupt deve essere resetta to ed il sistema deve riprendere la ricerca di un'altra avvenuta conversione.

In Fig. 5 è riportato il circuito che permette di effettuare le operazioni su indicate, mentre in Fig. 6 è riportato lo schema completo di questo modo di acquisizione.

FIG. 5 - Circuito di identificazione dell'ADC che ha converti to un evento, con modo di sele zione degli ingressi dei demul tiplexer relativamente all'ADC riconosciuto.

FIG. 6 - Schema elettrico del circuito di acquisizione random.

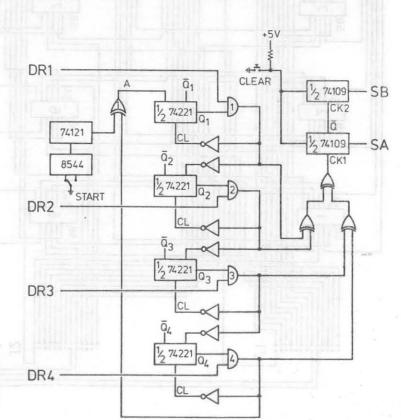

Vediamo ora in dettaglio il funzionamento del circuito di Fig. 5. Il pulsante di START provvede a lanciare un segnale A di durata opportuna che genera su  $Q_1$  un impulso positivo.

Se sulla linea DR1 è già presente un livello basso, il che sta ad indicare che l'ADC1 ha effettuato una conversione, il segnale A non si presenterà all'uscita dell'AND1 fino a che non sarà gestito l'interrupt inviato dalla combinazione dei segnali DR1 e  $\overline{Q}_1$  mediante il circuito di Fig. 7. Poichè  $S_B$  ed  $S_A$  sono negli stati zero, perchè azzerati prima dello start, all'uscita dei demulti plexer di Fig. 6 verso il registro d'ingresso della DR11-C saranno presenti i dati relativi al primo convertitore (ve dere Tabella I).

FIG. 7 - Circuito di richiesta d'interrupt.

## TABELLA I

| O efform | USCITE        | $s_{B}$ | $s_A$ | ADC<br>INDIRIZZATO |

|----------|---------------|---------|-------|--------------------|

| CLEAR    | +             | 0       | 0     | 1 2 major 1        |

| AND1     | 3. Tuga       | 0       | 1     | 2                  |

| AND2     | t to          | 1       | 0     | 3                  |

| AND3     | une officient | 1       | 1     | 4                  |

| AND4     | t             | 0       | 0     | 1                  |

FIG. 8 - Circuito di reset dello ADCn a lettura avvenuta.

Il segnale di DATA TRANSMITTED proveniente dalla DRII-C ad acquisizione avvenuta provvederà a resettare l'ADC1 ed a mandare DR1 alto (Fig. 8). Questo porterà alta l'uscita dell'AND1.

La stessa condizione di uscita alta all'AND1 si avrà se su DR1 non è presente un livello basso, il che sta ad indicare che l'ADC1 non ha effettuato fino a quell'istante alcuna conversione. Il risultato sarà in entrambi i casi il seguente:

- a) Q<sub>1</sub> torna basso perchè si presenta un impulso negativo sull'ingresso di CLEAR del monost<u>a</u> bile relativo;

- b) su Q2 si presenta un impulso positivo;

- c) SA passa dallo stato zero allo stato uno (vedere Tabella I).

Un livello basso su DR1 non verrà riconosciuto se il segnale A si sarà già presentato all'uscita dell'AND1, ma verrà gestito al passaggio successivo, cioè dopo che saranno testati i convertitori rimanenti.

Se supponiamo che sia sempre il segnale A a viaggiare lungo le uscite degli AND presenti in Fig. 5, per gli AND 2, 3, 4 vale la stessa sequenza dei segnali espressa per l'AND1. In altri termini, i convertitori vengono testati in sequenza, riprendendo il test dopo il quarto dal

primo, e viene gestito il trasferimento dei dati dal convertitore che volta per volta si presenta con una avvenuta conversione.

In particolare, all'uscita dei demultiplexer è presente volta per volta il dato dell'ADC che effettua la richiesta d'interrupt perchè  $\mathbf{S}_{B}$  ed  $\mathbf{S}_{A}$  cambiano di stato con la sequenza riportata in Tabella I.

Il segnale generato dallo START deve essere di durata tale da esaurirsi prima che il segnale alto A si presenti all'ingresso dell'EXOR1, nell'ipotesi che il tempo di effettuazione di un giro completo sia minimo e cioè che nessun ADC abbia effettuato una conversione. Se nessun ADC ha convertito la sequenza si ripete in media ogni 300 nanosecondi.

Le uscite  $Q_n$  (n = 1,2,3,4) devono presentare un segnale alto di durata maggiore dell'intervallo di tempo che va dall'istante in cui  $\overline{Q}_n$  va basso, all'istante in cui DRn torna alto. Intervallo durante il quale il calcolatore deve gestire l'interrupt, registrare il dato, generare il DATA TRANSMITTED.

Gli invertitori presenti su ciascun ANDn hanno la funzione di ritardare il segnale A per permettere il cambio di  $S_B$  ed  $S_A$  prima dello azzeramento del monostabile con uscita  $Q_n$  e del cambio di stato di quello con uscita  $Q_{n+1}$ . Questo assicura che i dati presenti all'uscita dei de multiplexer appartengono al convertitore che fa richiesta d'interrupt.

L'utilizzo dei convertitori a 12 bit ed il registro d'ingresso della DR11-C a 16 bit permet tono di avere quattro bit disponibili per ogni dato in ingresso al calcolatore. Pertanto, alla parola a dodici bit, si aggiungono due bit collegati ad  $S_{\rm B}$  ed  $S_{\rm A}$  che permettono successivamente via programma di risalire all'ADC che ha generato quel dato. Altri due bit restano disponibili per l'acquisizione di altrettanti segnali logici eventualmente connessi all'evento.

Infine, anche in questo sistema di acquisizione, un flag settabile via hardware e testato ad ogni sequenza di lettura, provvede a segnalare la fine della misura in corso.

## 2. - CONVERTITORI ANALOGICO-DIGITALI.

Per la parte di conversione sono stati utilizzati quattro ADC modello 7411/N a dodici bit della Silena. Tali convertitori, di tipo Wilkinson general purpose, hanno un tempo di conversione che può essere fissato a 34 microsecondi, indipendentemente dal valore del segnale in ingresso da convertire, oppure può essere variabile dipendente dal valore del segnale in ingresso secondo la relazione (1.28+0.01 N) microsecondi essendo N il canale convertito.

La loro logica è negativa per i segnali di gestione in uscita, mentre è positiva per quelli in ingresso.

Il segnale analogico in ingresso deve essere di polarità positiva con un valore nel range da 20 millivolt a 8.2 volt su 1 Kohm di impedenza d'ingresso.

Il registro d'uscita è costituito da gate di trasferimento a tre stati, per cui il trasferimento stesso è possibile solo se è presente un livello alto sull'ingresso DATA ENABLE. Per la nostra utilizzazione questo ingresso è stato collegato direttamente ad un livello positivo affinchè i

dati in uscita siano sempre disponibili per la registrazione da parte del calcolatore.

La combinazione della loro linearità differenziale ed integrale e della buona stabilità li rende particolarmente adatti per applicazioni di spettroscopia nucleare a tassi di conteggio non particolarmente elevati.

Potendosi valutare in 1 microsecondo il tempo di trasferimento al calcolatore di un evento convertito, il tempo morto sia per il caso di acquisizione multiparametrica che per il caso di acquisizione random non supera i 35 microsecondi per evento, quasi totalmente a carico del l'ADC. Sono perciò possibili tassi di acquisizione di parecchi KHz senza particolari problemi.

Ringraziamo il dott. A. Pantaleo della Sezione INFN di Bari per i costruttivi colloqui sul le finalità e sulla flessibilità d'uso del sistema realizzato, nonchè per il costante incoraggiamento nelle varie fasi della realizzazione.

datt in uscita sinno sempre disponibili per in registrazione da parte del calculatore,

La combinazione della loro linearità differenziale ed integrale e della quona stabilità il rende particolarmente adalti per applicazioni di apeltroscopia mucleare a tassi di conteggio non particolarmente elevati.

Potendosi valitare in i microsecondo il cempo di franferimento al calcolatore di un cven to convertito, il tempo morto ala per il caso di acquisizione multiparametrica cut pur il caso di acquisizione random non supera i 35 microsecondi per evento, quani totalmenta è carico del l'ADC. Sono perciò possibili tassi di acquisizione di parecchi KHz sonza particolari problemi.

Ringraziamo il dott, A. Pentaleo della Sezione IMEN di Bari per i contruttvi colloqui sul le finalità e sulla flessibilità d'uso del atstema realizzato, nonche per il contante incoraggiamento nelle varie inal della realizzazione.