# ISTITUTO NAZIONALE DI FISICA NUCLEARE

Sezione di Napoli

INFN/TC-06/12 14 Settembre 2006

## UN OPERAZIONALE FULL CUSTOM IN TECNOLOGIA 0.35 MICRON

P. Parascandolo<sup>1</sup>, V. Sipala <sup>2</sup>

1) INFN Sezione di Napoli 2) INFN Sezione di Catania

#### **Abstract**

Nella progettazione analogica full custom il progettista lavora a livello del transistor singolo sia nel disegno dello schema elettrico che nella definizione del corrispondente layout. A partire da determinate specifiche, il progettista sceglie lo schema elettrico che meglio risponda alle richieste. Si dimensionano i singoli transistor e se ne simula il comportamento. Stabilite le caratteristiche elettriche del progetto si passa alla realizzazione del layout, vale a dire del disegno che permette la definizione delle maschere per l'implementazione del circuito sul silicio.

Questa nota descrive la progettazione con calcoli analitici dello schema elettrico di un amplificatore operazionale e le simulazioni dello stesso, utilizzando il programma "Virtuoso" proprietario di Cadence e confronta i risultati delle simulazioni con il calcolo teorico. L'amplificatore è un VLSI (Very Large Scale Integration) realizzato in tecnologia CMOS da 0.35 micron dalla AMS (AustriaMicroSystems 2).

#### 1. INTRODUZIONE

La quasi totalità dei progettisti analogici usa SPICE come programma di simulazione. La prima versione di SPICE (SPICE1) fu sviluppata a Berkeley nel 1972 e fu distribuito liberamente. Il modello di Shichmann-Hodges per il MOSFET è derivato direttamente dallo SPICE1 di Berkeley. Le equazioni di questo modello (LEVEL1) sono relativamente semplici, ed è per questo motivo che è ancora usato nella maggior parte dei libri di testo. Esso è molto utile per fare dei calcoli a mano che descrivono con una discreta approssimazione (entro il 10%) dispositivi con lunghezza di canale fino al micron; ma, con il diminuire delle dimensioni dei transistori, è stato necessario sviluppare modelli più accurati. Attualmente il modello BSIM3v3 è quello più diffuso per dispositivi con lunghezza di canale al di sotto del micron.

Per la progettazione full custom la disponibilità di accurati modelli per il MOSFET è fondamentale.

La Sezioni INFN di Napoli e Catania sono iscritte al consorzio europeo di Europractice ed hanno la full suite di Cadence con l'hit kit dell'AMS (Austrian MicroSystem) per la progettazione analogica. In ambiente Cadence, una volta disegnato lo schematico, per la simulazione analogica viene utilizzato SPECTRE [1].

Questa nota descrive una metodologia di progetto per un amplificatore operazionale a due stadi con un OTA (Operational Trasconductance Amplifier) nello stadio d'ingresso ed un amplificatore a CS (Common Source) compensato in frequenza sul secondo stadio per pilotare un carico di uscita puramente capacitivo.

### 2.1. L' OTA

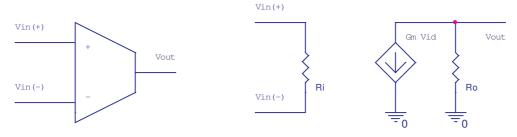

Il simbolo ed il modello per il circuito equivalente dell'amplificatore operazionale a trasconduttanza (OTA) [2] sono mostrati in **Figura 1**:

Fig. 1 Simbolo e circuito equivalente di un OTA

L'OTA converte una tensione differenziale  $V_{ID}$  in ingresso in una corrente  $G_m \cdot V_{ID}$  in uscita e quindi la funzione di trasferimento di un OTA dipende dalla sua trasconduttanza  $G_m$ . Idealmente, la resistenza di ingresso Ri e quella di uscita Ro sono infinite ( $Ri = Ro = \infty$ ).

L'OTA convenzionale è un amplificatore in classe A con una corrente di ingresso eguale a zero e una corrente di uscita pari a  $G_m \cdot V_{ID}$ . La tensione di uscita è data dalla relazione:

$$V_{out} = G_m \cdot V_{ID} \cdot Ro$$

mentre il guadagno in tensione è  $A = G_m \cdot Ro$

Poiché il nodo di uscita è ad alta impedenza, applicando un resistore di carico  $R_L$ , il guadagno dell'OTA diventa  $G_m \cdot (Ro//R_L) = G_m \cdot R_L$  e cioè peggiora.

I parametri che definiscono un OTA sono: Guadagno ad anello aperto  $(A_{OL})$ ; Prodotto Guadagno Banda passante (GB); Massima corrente di uscita  $(I_{OUTMAX})$ ; Slew-Rate (SR); Dissipazione statica  $(P_{STATIC})$ ; Margine di Fase (PHM); Tensione di Offset  $(V_{OS})$ ; Dinamica di uscita; Tensione di modo comune d'ingresso (ICMR); Rumore.

Il primo stadio dell'amplificatore operazionale effettua la conversione del segnale differenziale d'ingresso in un segnale single ended. È realizzato mediante una coppia differenziale d'ingresso con transistor PMOS o NMOS, a seconda delle specifiche di progetto.

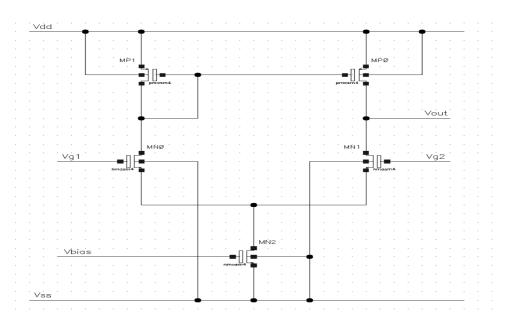

Nell'OTA single ended di **Figura 2**, alimentato in modo simmetrico con Vdd = |Vss|, la coppia differenziale è in tecnologia NMOS ed è costituita dai transistor  $M_{N0}$  ed  $M_{N1}$  aventi lo stesso fattore di forma  $(W_{MN0}/L_{MN0} = W_{MN1}/L_{MN1})$ .

Fig. 2 L'amplificatore a trasconduttanza:coppia differenziale a carico attivo

Il carico della coppia differenziale è un "carico attivo" costituito dalla coppia di transitor  $M_{P0}$  -  $M_{P1}$  a specchio di corrente. La configurazione a carico attivo consente di ottenere un guadagno elevato senza esser costretti ad integrare delle resistenze di valore elevato ottimizzando così l'occupazione dell'area di silicio. I fattori di forma dei transistor dello specchio sono in genere gli stessi ( $W_{MP0}/L_{MP0} = W_{MP1}/L_{MP1}$ ) in modo che la corrente che scorre sui due rami sia identica. In questa configurazione, tuttavia, il circuito non è simmetrico: non si può applicare la tecnica del mezzo circuito per il modo differenziale ma si può ragionevolmente assumere che i source di  $M_{N0}$  ed  $M_{N1}$  costituiscano una massa virtuale se vengono applicati piccoli segnali d'ingresso di puro modo differenziale.

Il transistor  $M_{N2}$  funziona da generatore di corrente. Per piccoli segnali differenziali d'ingresso la corrente  $I_{SS}$  che scorre in  $M_{N2}$ , controllata dalla tensione  $V_{bias}$ , è abbastanza indipendente dalla tensione di modo comune applicata agli ingressi.

L'analisi in DC rivela che se  $V_{G1}$ , tensione di gate del transistor  $M_{N0}$ , è molto più negativa di  $V_{G2}$ ,  $M_{N0}$  è spento. Su  $M_{N0}$  non scorre corrente, quindi, la corrente attraverso  $M_{P1}$

e  $M_{P0}$  è nulla. Quando  $V_{G1}$  si approssima a  $V_{G2}$ ,  $M_{N0}$  si accende e la corrente  $I_{SS}$  che attraversa  $M_{N2}$  si divide tra  $M_{N0}$  ed  $M_{N1}$ . In assenza di segnale differenziale d'ingresso, con i transistor tutti in saturazione la corrente  $I_{SS}$  si suddivide in due parti eguali. Se invece  $V_{G1}$  è molto più positiva di  $V_{G2}$ ,  $M_{P0}$  va nella regione a triodo,  $M_{N1}$  si spegne e la tensione di uscita si approssima a  $V_{DD}$ .

Applicando un segnale di puro modo differenziale  $V_{ID} = V_{G1} - V_{G2}$ , assumendo che le alimentazioni siano dei corti per il segnale, la tensione applicata si può esprimere come una variazione bilanciata di  $+V_{ID}/2$  su  $M_{N0}$  e  $-V_{ID}/2$  su  $M_{N1}$ . Le variazioni di tensioni sui gate, fanno variare le correnti di drain di  $M_{N0}$  ( $g_{m0} \cdot V_{ID}/2$ ) e di  $M_{N1}$  ( $-g_{m1} \cdot V_{ID}/2$ ).

Poiché il segnale in corrente su  $M_{N0}$  è lo stesso di quello su  $M_{P1}$ , e poiché questo viene copiato su  $M_{P0}$ , il segnale in corrente sul nodo di uscita vale  $(-g_{m0} \cdot V_{ID}/2) + (-g_{m1} \cdot V_{ID}/2)$ . Ma, essendo  $g_{m0} = g_{m1} = g_m$ , risulta che  $I_{OUT} = -g_m V_{ID}$  e cioè la trasconduttanza  $G_m$  di tutto lo stadio è:

$$G_{m} = \frac{\delta I_{OUT}}{\delta V_{ID}} \cong \sqrt{K_{1}^{'} \cdot I_{SS} \cdot (W_{1}/L_{1})}$$

dove  $K_1$  è una costante che dipende dalla tecnologia. La resistenza di uscita è  $Ro = (ro_{MP0} / ro_{MN1})$  e il guadagno differenziale in assenza di carico è pari a:

$$A \cong G_m \cdot (ro_{MP0} // ro_{MN1})$$

Come si vede, l'amplificazione del primo stadio dipende in modo rilevante dalle impedenze intrinseche di  $M_{P0}$  ed  $M_{N1}$ . Queste impedenze sono elevate quando i dispositivi sono in saturazione e modeste quando i transistor lavorano nella zona a triodo.

## 2.2. LA TENSIONE D'INGRESSO DI MODO COMUNE (ICMR)

Per determinare l'ICMR si pone  $V_{ID}$ =0 collegando insieme gli ingressi e si varia la tensione applicata  $V_{IC}$  nei due versi fino a che uno dei transistor è fuori dalla zona di saturazione. La massima tensione di modo comune applicabile  $V_{IC(MAX)}$  dipende dai transistor  $M_{P0}$  ed  $M_{P1}$  in quanto questi possono uscire dalla saturazione. In questa fase il transistor  $M_{N2}$  è relativamente ininfluente. Ci sono due maglie da analizzare: la prima maglia va dal gate di  $M_{N0}$  via  $M_{P1}$  a  $V_{DD}$ .

$V_{IC(MAX)} = V_{G1(MAX)} = V_{DD} - V_{GSMP1} - V_{DSMN0} + V_{GSMN0}$  ma, al limite della saturazione  $V_{DS} = V_{GS} - V_T$  e perciò  $(-V_{DS} + V_{GS}) = V_T$ . Quindi:

$$\begin{split} V_{IC(MAX)} = \ V_{DD} - V_{GSMP1} + V_{TMN0.} \\ La seconda maglia va dal gate di <math>M_{N1}$$

via  $M_{P0}$  a  $V_{DD}$ . Perciò:

$V_{IC(MAX)} = V_{DD} - V_{DSMP0(sat)} - V_{DSMN1} + V_{GSMN1} = V_{DD} - V_{DSMP0(sat)} + V_{TMN1} \\ Il caso peggiore ~ (V_{IC(MAX)} inferiore) si ha nel percorso della prima maglia. \\ La tensione di modo comune <math>V_{IC}$  più bassa applicabile  $V_{IC(MIN)}$  risulta limitata dal generatore di corrente  $M_{N2}$  che può uscire dalla saturazione:

$$V_{IC(MIN)} = V_{SS} - V_{DSMN2(sat)} - V_{GSMN0} = V_{SS} - V_{DSMN2(sat)} - V_{GSMN1}$$

La tensione di ingresso di modo comune applicabile è in genere una specifica progettuale ed i valori di  $V_{IC(MAX)}$  e  $V_{IC(MIN)}$  possono essere usati per calcolare i fattori di forma dei transistor della coppia differenziale e del carico attivo.  $V_{IC(MAX)}$  può essere usato per calcolare il fattore di forma (W/L) di  $M_{Pl}$  montato a diodo;  $V_{IC(MIN)}$  può essere usato per i fattori di forma di  $M_{N0}$  ed  $M_{N1}$ .

#### 2.3 LA DINAMICA DI USCITA DEL PRIMO STADIO

Come abbiamo visto, il massimo del guadagno lo si ottiene quando  $M_{N1}$  ed  $M_{P0}$  sono in saturazione. Con  $V_{ID}$  = 0,  $M_{N1}$  è in saturazione quando:

$$V_{DSMN1} \geq V_{GSMN1} - V_{TN} \label{eq:VDSMN1}$$

poiché  $V_{DMN1} = V_{OUT}$  e  $V_{GMN1} = V_{IC}$  , abbiamo:

$$V_{OUT} - V_{SMN1} \ge V_{IC} - V_{SMN1} - V_{TN}$$

ossia:

$$V_{OUT} \ge V_{IC} - V_{TN}$$

[1]

M<sub>P0</sub> è in saturazione quando si verifica la seguente relazione:

$$V_{DSMP0} \ge V_{GSMP0} - |V_{TP}|$$

cioè:

$$V_{DD-}V_{OUT} \ge V_{GSMP0} - |V_{TP}|$$

da cui:

$$V_{OUT} \le V_{DD} - V_{GSMP0} + |V_{TP}|$$

[2]

La dinamica dell'amplificatore è perciò compresa tra i limiti delle equazioni [1]  $V_{OUT(max)}$  e [2]  $V_{OUT(min)}$ .

## 2.4. L'AMPLIFICATORE A DUE STADI

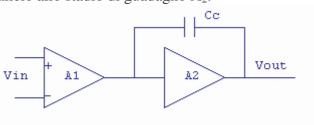

In generale, per raggiungere livelli di guadagno elevati, sarà necessario mettere in cascata più stadi di amplificazione. Lo schema classico di amplificatore a due stadi (detto anche di Miller) è mostrato in **Figura 3** dove è stato introdotto il condensatore di compensazione in parallelo allo stadio di guadagno A<sub>2</sub>.

Fig. 3 Schema di un amplificatore a due stadi

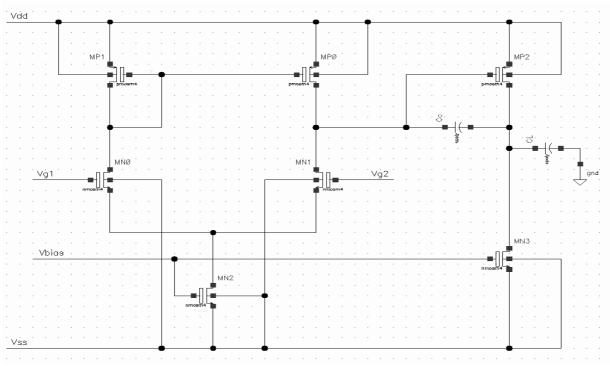

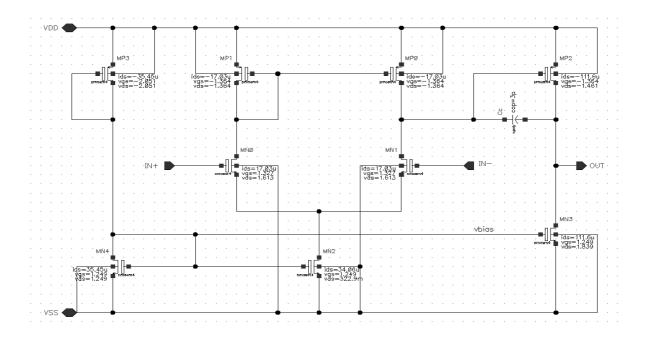

Una possibile implementazione dello schema a blocchi di **Figura 3** è mostrata in **Figura 4** dove sono stati inseriti i due transistor  $M_{N3}$  ed  $M_{P2}$  e non è stato inserito il buffer di uscita perché si pilota un carico puramente capacitivo. Il guadagno di questa configurazione è dato dal prodotto dei guadagni dei due blocchi:

$$A_{vo} = A_{v1} \cdot A_{v2}$$

e dipende pesantemente dalla frequenza. Stimiamo dapprima il guadagno a frequenze prossime alla DC, dove possiamo anche trascurare l'effetto della capacità  $C_c$ . Il primo stadio (ved **Figura. 4**) è uno stadio differenziale con carico attivo che pilota un carico di resistenza infinita (il gate di  $M_{P2}$ ) e quindi rimane solo il carico intrinseco:

$$A_{v1} = g_{m1} \cdot (ro_{MP0} // ro_{MN1})$$

dove  $ro_{MP0}$  e  $ro_{MNI}$  sono rispettivamente resistenza di uscita del transistor  $M_{P0}$  e  $M_{N1}$ .

Il secondo stadio è uno stadio a source comune, che ha come carico ancora una resistenza infinita (il condensatore  $C_L$ ) e, quindi, ha un guadagno pari a:

$$A_{v2} = g_{mMP2} \cdot \left( ro_{MP2} // ro_{MN3} \right)$$

Fig. 4 Amplificatore a due stadi

## 2.5. LA RISPOSTA IN FREQUENZA E SLEW-RATE

La risposta in frequenza dell'amplificatore a 2 stadi è volutamente dominata dalla presenza della capacità  $C_c$  (capacità di compensazione) in controreazione sul secondo stadio che crea il polo dominante e stabilizza la risposta in frequenza dell'operazionale.

Detto  $|T(j\omega)|$  il guadagno di anello, dalla teoria della reazione è noto che se  $|T(j\omega)|>1$  alla frequenza per cui per cui  $\Phi$   $|T(j\omega)|=-180^\circ$ , l'operazionale non è stabile. Poiché ciascun polo introduce uno sfasamento di -90°, è evidente che un circuito a più poli può facilmente

diventare instabile mentre invece un circuito con solo un polo ed una rete di retroazione indipendente dalla frequenza è incondizionatamente stabile.

La capacità  $C_c$  è soggetta ad effetto Miller (perché fra i suoi nodi c'è uno stadio con guadagno  $-A_{v2}$ ) e diventa, quindi, la capacità dominante del circuito per frequenze intermedie. Per effetto del condensatore  $C_c$  il guadagno  $A_{v1}$  cambierà, poiché il primo stadio (OTA) vedrà come carico l'impedenza finita introdotta dalla capacità  $C_c$  amplificata a causa dell'effetto Miller. Questa capacità vale:

$$C_{eq} = C_c \cdot (1 + Av_2) \cong C_c \cdot Av_2$$

Il guadagno A<sub>v1</sub> diventa quindi:

$$A_{v1} = g_{m1} \left[ (ro_{MP0} // ro_{MN1}) // \left( \frac{1}{sC_{eq}} \right) \right]$$

A frequenze intermedie C<sub>eq</sub> domina. Quindi:

$$A_{v1} = \left(\frac{g_{m1}}{sC_{eq}}\right) = \left[\frac{g_{m1}}{\left(sC_c \cdot A_{v2}\right)}\right]$$

Il guadagno totale è dato dal prodotto dei due blocchi

$$A_{vo} = A_{v1} A_{v2} \cong (g_{m1}/sC_c A_{v2}) A_{v2} \cong g_{m1}/sC_c$$

La frequenza per cui il guadagno A<sub>vo</sub> diventa unitario è

$$\omega_{\rm t} = g_{\rm m1} / C_{\rm c}$$

Il prodotto guadagno banda passante (GB) vale quindi:

$$GB = g_{m1} / (2 \pi C_c)$$

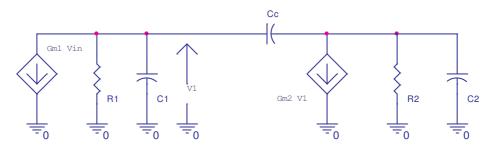

Per scegliere il valore di C<sub>c</sub> occorre conoscere la locazione dei primi due poli ma anche quella dello zero. I nodi che introducono i poli di interesse sono quello di ingresso al secondo stadio (dove compare la capacità di C<sub>c</sub> moltiplicata dall'effetto Miller) ed il nodo di uscita del secondo stadio (dove compare un'elevata resistenza). Il circuito equivalente per piccoli segnali è:

Fig. 5 Circuito equivalente amplificatore a 2 stadi

I parametri del modello sono:

$$\begin{array}{lll} R_1 = & ro_{MP0} /\!\!/ & ro_{MN1} & R_2 = & ro_{MP2} /\!\!/ & ro_{MN3} \\ C_1 = & C_{BDMP2} + C_{BDMN1} + C_{GSMP2} & C_2 = & C_{DBMP2} + C_{DBMN3} + C_L \end{array}$$

dove  $C_L$  rappresenta la capacità di carico del secondo stadio,  $C_{BD}$  la capacità tra bulk e drain dei diversi transistor,  $C_{GS}$  la capacità tra gate e source.

I poli e lo zero si ricavano confrontando l'equazione del circuito con quella generica:

$$A(s) = \frac{\left(1 + s/\omega_z\right)}{\left(1 + s/\omega_{p1}\right)\left(1 + s/\omega_{p2}\right)}$$

Nell'ipotesi che  $g_{mMP2} \cdot R_2 >> 1$  e che  $C_c >> C_1$ ,  $C_2$  si ha:

$$\begin{array}{ll} \omega_{p1} & \cong \ 1 \ / \ (g_{mMP2} \ R_1 \ R_2 \ C_c) \\ \omega_{p2} & \cong \ g_{mMP2} \ / \ (C_1 + C_2) \\ \omega_z & \cong \ -g_{mMP2} \ / \ C_c \end{array}$$

All'aumentare di g $_{mMP2}$  i due poli si separano (pole splitting) ed aumenta la stabilità. La presenza dello zero però complica le cose in quanto introduce sfasamenti negativi. L'introduzione di una resistenza  $R_c$  (che nel nostro caso non è stata necessaria) in serie alla capacità  $C_c$  non ha quasi effetto sul valore dei poli ma cambia il valore dello zero (spostandolo in avanti) e si può quindi inserirla per migliorare la stabilità.

Lo slew-rate è il massimo gradiente che può assumere l'uscita in presenza di variazioni brusche (idealmente infinite) dell'ingresso. Questa limitazione nasce dal fatto che la massima corrente che il primo stadio può fornire al secondo stadio coincide con la corrente di polarizzazione  $I_{SS}$ . Quando l'ingresso ha delle variazioni brusche ed ampie l'intera corrente di polarizzazione scorre solo in uno dei due transistor d'ingresso è tale corrente è l'unica disponibile per caricare o scaricare la capacità di compensazione  $C_c$ . Perciò:

$$SR = \delta V_{out} / \delta V_{in} = I_{SS} / C_c$$

In genere lo slew rate è una specifica di progetto che ci consente di dimensionare il generatore di corrente fatto con il transistor  $M_{\rm N2}$ .

### 3. IL PROGETTO DELL'OPERAZIONALE A DUE STADI

Poiché il modello matematico del MOS è abbastanza complicato, il calcolo teorico consente solo una buona stima della funzionalità del progetto. Per ottenere una precisione elevata l'uso del calcolatore è indispensabile.

Sulla base delle considerazioni sin qui effettuate, progettiamo un amplificatore operazionale a due stadi con un margine di fase di 60° con le seguenti specifiche:

$$\begin{array}{lll} A_{vo} > 5000 \; \text{V/V} & V_{DD} = 1.65 \; \text{V} & V_{SS} = -1.65 \; \text{V} \\ GB \ge 5.5 \; \text{MHz} & C_L = \; 11.5 \; \text{pF} & SR > 10 \; \text{V/}\mu\text{S} \\ V_{out \; (range)} = \; \pm 1 \; \text{V} & ICMR = -0.5 \; \text{to} \; 1.1 \text{V} & P_{diss} \le \; 2 \; \text{mW} \end{array}$$

Usando il programma di disegno e simulazione della Cadence con l'hit kit 3.70 dell'AustriaMicrosystem (AMS), progettiamo l'amplificatore in tecnologia CMOS 0.35 micron. Nell'ipotesi che il source sia cortocircuitato con il substrato, assumiamo le seguenti costanti tecnologiche:

-Tensione di soglia  $V_{th} = 530 \text{mV} \pm 5\%$  (per NMOS) e  $V_{th} = 730 \text{mV} \pm 5\%$  (per PMOS)

-Fattore di guadagno  $K'_{N} = 140 \cdot 10^{-6} \, \mu \text{A/V}^{2} \text{ e } K'_{P} = 25 \cdot 10^{-6} \, \mu \text{A/V}^{2}.$

Per quanto attiene al valore di  $\lambda$  assumiamo:

$$\lambda_P = 0.05 \text{ e } \lambda_N = 0.04 \text{ nel caso che (Vds} \ge Vds(sat) + 500 \text{mV}).$$

Iniziamo con la scelta della capacità di compensazione C<sub>c</sub> dove applichiamo una cosiddetta "rule of thumb" e cioè che per ottenere il margine di fase di 60° si richiede:

$$C_c \ge (0.22 \cdot C_L)$$

$$g_{\text{mMP2}} \ge (10 \cdot g_{\text{mMN0}})$$

ed anche:

Poiché da specifica progettuale abbiamo un carico C<sub>L</sub> da 11.5 pF:

$$C_c = 0.22 \cdot 11.5 \, pF = 2.53 \, pF$$

Scegliamo un condensatore un poco più grande da 3pF. Un condensatore esageratamente più grande occuperebbe una rilevante area di silicio e perciò è da evitare.

Dalla definizione dello slew-rate possiamo dedurre la corrente I<sub>SS</sub>:

$$I_{SS} = C_c \cdot SR = (3.10^{-12}) \cdot (10/10^{-6}) = 30 \mu A$$

La corrente Iss assieme all'ICMR entra nel dimensionamento di tutto il primo stadio. Dalla dinamica d'ingresso richiesta (ICMR= -0.5 to 1.1V) ricaviamo il fattore di forma per il transistor  $M_{Pl}$ :

$$\left(\frac{W}{L}\right)_{MP1} = \frac{I_{SS}}{K_{MP1}^{'} \left[V_{DD} - V_{in(max)} - \left|V_{TP}\right|_{(max)} + V_{TN(min)}\right]^{2}} = \frac{30 \cdot 10^{-6}}{\left(25 \cdot 10^{-6}\right) \left[1.65 - 1.1 - 1.05 + 0.79\right]^{2}} = 15$$

Per ottenere due rami simmetrici poniamo  $(W/L)_{MP0} = (W/L)_{MP1} = 15$ . Noto il GB dell'operazionale, possiamo ricavare il valore della transcoduttanza di  $M_{N1}$ :

$$g_{m1} = 2\pi \cdot GB \cdot C_c$$

$g_{m1} \approx 6.28 \cdot (5.5 \cdot 10^6) (3 \cdot 10^{-12}) \approx 103.6 \mu S$

Da questo valore possiamo determinare i fattori di forma di M<sub>N0</sub> ed M<sub>N1</sub>:

$$\left(\frac{W}{L}\right)_{MN0} = \left(\frac{W}{L}\right)_{MN1} \approx \frac{g_{m1}^2}{K_{MN1}^{'} \cdot I_{SS}} \approx \frac{\left(103 \cdot 10^{-6} \,\mu\text{S}\right)^2}{\left(140 \cdot 10^{-6} \,\mu\text{A}/V^2\right) \cdot \left(30 \cdot 10^{-6} \,\mu\text{A}\right)} \approx 2.56$$

Scegliamo  $(W/L)_{MN0} = (W/L)_{MN1} = 3$ . Bisogna adesso dimensionare  $M_{N2}$ , che funziona da generatore di corrente, usando la specifica di ICMR (la tensione d'ingresso minima). Abbiamo in precedenza ricavato l'eguaglianza:

$$V_{DSMN2} = V_{in} - V_{SS} - V_{GSMN1}$$

Sappiamo, inoltre, che:  $V_{GSMN1} = [I_{SS} / K'_{NM2} \cdot (W/L)]^{1/2} - V_{TNM1}$

quindi, ricaviamo:

$$V_{DSMN2} = V_{in(min)} - Vss - (I_{SS} / \beta_1)^{1/2} - V_{TN(max)}$$

con  $\beta_1$  = K'<sub>MN1</sub> • (W/L)<sub>MN1</sub> = (140•10<sup>-6</sup>  $\mu$ A/V<sup>2</sup>) • (3) = 420  $\mu$ A/V<sup>2</sup>. Possiamo quindi calcolare:

$\begin{array}{c} V_{DSMN2} = \ \ (\text{-}0.3)\text{-}(\text{-}1.65) - [(30 \text{-}10^{\text{-}6}\ )\ /\ (420 \text{-}10^{\text{-}6}\ )\ ]^{1/2} \text{-} \ 0.85 = \ 0.24V \\ Con\ V_{DSMN2\,(sat)} = \ 280\text{mV}, \ essendo \ \ V_{DSMN2(sat)} = [2\ I_{SS}\ /\beta_1]^{1/2} \ \ ricaviamo: \end{array}$

$$\left(\frac{W}{L}\right)_{MN2} = \frac{2I_{SS}}{K'_{MN1}(V_{DSMN2})^2} = \frac{60 \cdot 10^{-6}}{\left(140 \cdot 10^{-6} \,\mu\text{A}/V^2\right) \cdot \left(0.24\right)^2} = 7.3$$

Scegliamo (W/L)<sub>MN2</sub> = 7.

Infine scegliamo le dimensioni dello stadio di uscita. Scegliamo di imporre che  $V_{GSMP0}$  sia eguale a  $V_{GSMP2}$ . Perchè il margine di fase di  $60^{\circ}$  dobbiamo rispettare le due relazioni:

$$C_c \ge (0.22 \cdot C_L)$$

e  $g_{mMP2} \ge (10 \cdot g_{mMN0})$

Moltiplichiamo membro a membro:

$$g_{\text{mMP2}} C_c = 2.2 \bullet g_{\text{mMN0}} \bullet C_L$$

e ricaviamo:

$$g_{\text{mMP2}} = 2.2 \cdot g_{\text{mMN0}} (C_L / C_c) = 2.2 \cdot 103 \cdot (11.5/3) = 867 \,\mu\text{S}$$

Essendo poi V<sub>GSMP0</sub> eguale a V<sub>GSMP2</sub>, dal rapporto tra le due trasconduttanze:

$$g_{\text{mMP2}} / g_{\text{mMP0}} = \beta_{\text{MP2}} / \beta_{\text{MP0}}$$

ricaviamo il fattore di forma di M<sub>P2</sub>:

$$(W/L)_{MP2} = (W/L)_{MP0} \cdot (g_{mMP2} / g_{mMP0}) = 15 \cdot (867/103) = 125$$

Adesso stimiamo la corrente che scorre in M<sub>P2</sub>

$$I_{MP2} = \frac{g^2_{mMP2}}{2 \cdot K'_{MP2} \cdot (W/L)_{MP2}} = \frac{(867 \cdot 10^{-6})^2}{2 \cdot (25 \cdot 10^{-6} \, \mu A/V^2) \cdot (125)} = 120 \, \mu A$$

Rimane da calcolare il fattore di forma del transistor  $M_{N3}$ . Poiché questo da disegno ha la stessa tensione di gate di  $M_{N2}$ , il rapporto tra le correnti corrisponde a quello dei fattori di forma. Cioè:

$$(W/L)_{MN2} = (W/L)_{MN2} \cdot (I_{MN3}/I_{SS}) = 4.5 \cdot (125/30) \approx 29$$

Poiché le resistenze intrinseche dei transistor sono esprimibili come  $r_0=1/(\lambda \cdot I)$ , l'amplificazione che è il prodotto delle amplificazioni dei due stadi, si può esprimere come:

$$A_{v} = \frac{2g_{mMN1}}{I_{SS} \cdot (\lambda_{MN1} + \lambda_{MP0})} \cdot \frac{g_{mMP2}}{I_{MP2} \cdot (\lambda_{MP2} + \lambda_{MN3})} =$$

$$= \frac{2 \cdot 103.6 \mu S}{(25 \cdot 10^{-6} \, A/V^{2}) \cdot (0.04 + 0.05)} \cdot \frac{867 \, \mu S}{125 \mu A \cdot (0.05 + 0.04)} = 7084$$

Per completare lo stadio è necessario creare la rete di polarizzazione per alimentare i transistor  $M_{N3}$  ed  $M_{N2}$ . Ciò è fatto con i due transistor  $M_{P3}$  e  $M_{N4}$ . La corrente assorbita in totale è  $I_{REF}$  +  $I_{SS}$  +  $I_{MP2}$  = (30 + 30 + 125)  $\mu A$  = 185  $\mu A$  e perciò abbiamo una potenza dissipata di 610  $\mu W$ .

Fig. 6 Schema elettrico dell'amplificatore operazionale progettato

#### 4. LE SIMULAZIONI

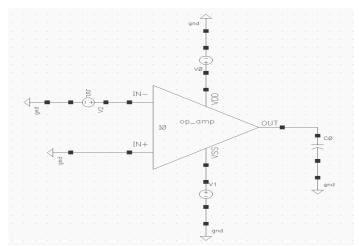

Una volta disegnato l'amplificatore se ne associa il simbolo e si costruisce una schema a livello gerarchico superiore (**Figura 7**) per effettuare le simulazioni (**Figura 8**).

Fig. 7 Schematico Top-Level

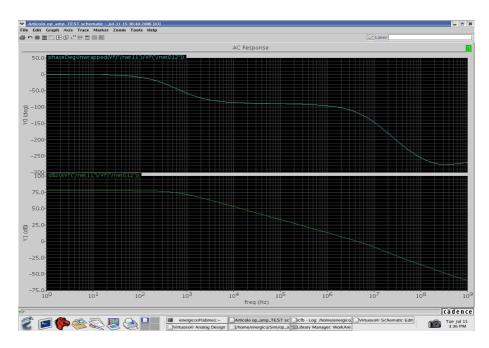

Prima di effettuare il layout vengono effettuate diverse simulazioni sia in DC in regime transitorio. In **Figura 8** è indicata la spazzolata in frequenza, da dove si vede che il guadagno in continua è 75 dB e il margine di fase è superiore a  $60^{\circ}$ .

La corrente Iss risulta di 34 μA, quella dello stadio di uscita di 110 μA.

Fig. 8 Diagramma di Bode dell'operazionale progettato

## 5. CONCLUSIONI

Questa nota ha mostrato una metodologia di progetto per un amplificatore operazionale full custom a due stadi in tecnologia da 0.35 micron.

I calcoli effettuati usando le formule tipiche per il LEVEL1 si discostano, come previsto, all'incirca del 10% rispetto ai risultati della simulazione pre-layout.

# 6. BIBLIOGRAFIA

- [1] K.S. Kundert "The designer's Guide to SPICE and SPECTRE" Wiley 1993.

- [2] P.R. Gray and R.G. Meyer "Analysis and Design of Analog Integrated Circuits" Wiley 1993.